# PhD Thesis

# Scheduling parallel real-time tasks in multiprocessor platforms

## Cláudio Maia

**CISTER-TR-181118**

2018/11/06

## Scheduling parallel real-time tasks in multiprocessor platforms

#### Cláudio Maia

\*CISTER Research Centre

Polytechnic Institute of Porto (ISEP-IPP)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8321159

E-mail: clrrm@isep.ipp.pt http://www.cister.isep.ipp.pt

## **Abstract**

### FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Scheduling Parallel Real-Time Tasks in Multiprocessor Platforms

Cláudio Roberto Ribeiro Maia

Doctoral Program in Electrical and Computer Engineering

Supervisor: Luís Miguel Pinho Nogueira

Co-Supervisor: Luís Miguel Rosário da Silva Pinho

November 6, 2018

## Scheduling Parallel Real-Time Tasks in Multiprocessor Platforms

## Cláudio Roberto Ribeiro Maia

Doctoral Program in Electrical and Computer Engineering

## Resumo

No passado era suficiente aumentar a frequência de execução em processadores mononúcleo, de modo a adicionar novas funcionalidades de *software*. No entanto, devido a limitações no meio físico, os fabricantes de processadores deixaram de fabricar processadores mononúcleo em favor de processadores multinúcleo. Enquanto, no âmbito geral, esta adaptação é benéfica para a indústria de *software*, dado que permite a inclusão de funcionalidades mais exigentes e complexas nas aplicações, a utilização de sistemas comerciais de *hardware* (conhecidos como COTS - *Commercial-Off-The-Shelf*) em ambientes de tempo-real apresenta um desafio ainda em aberto. De facto, em sistemas de tempo-real, a previsibilidade é considerada mais importante do que o desempenho e é um requisito para a exactidão, num domínio que é sobejamente conhecido pelos seus rigorosos requisitos temporais.

Podemos apontar duas razões principais para este desafio. Em primeiro lugar, as arquitecturas COTS são desenhadas para sistemas em que o desempenho no caso médio é importante, e por conseguinte, recursos como componentes de memória (*i.e.*, memória principal, memória *cache*, *etc.*), periféricos e barramentos, são partilhados entre os vários núcleos do sistema. Consequentemente, se não houver cuidado, desvios temporais, daqueles que foram estimados em tempo de desenho da aplicação, podem ocorrer (devido a interferência) sempre que núcleos diferentes acedem simultaneamente aos recursos partilhados do sistema. Em segundo lugar, a plataforma de *hardware* não só suporta execução concorrente ao nível dos núcleos, mas também suporta execução paralela ao nível da plataforma. Por conseguinte, o objectivo principal para a comunidade de sistemas de tempo-real é encontrar soluções eficientes para lidar com o comportamento paralelo e inerente à plataforma, e ao mesmo tempo, assegurar a previsibilidade das aplicações, tendo em consideração os recursos partilhados da plataforma. Nesta dissertação, este objectivo é dividido em dois problemas distintos que são abordados de forma independente, nomeadamente: (i) o problema de escalonamento de tarefas paralelas com restrições temporais em plataformas multiprocessador; (ii) o problema da partilha de recursos em plataformas multiprocessador.

O primeiro problema (o problema de escalonamento de tarefas paralelas com restrições temporais em plataformas multiprocessador) é coberto usando duas perspectivas diferentes. A primeira perspectiva foca-se no tempo de resposta de tarefas paralelas e de tempo-real utilizando o modelo síncrono de tarefas paralelas. O modelo considerado tem como alvo tarefas com prioridades fixas, compostas por vários segmentos, em que cada segmento é composto por um número arbitrário de unidades de execução independentes e que podem ser executadas em paralelo. Para alcançar este objectivo, novos conceitos, tais como decomposição do *carry-out* e janela deslizante, são introduzidos de modo a derivar um cenário no pior caso que permita computar o pior tempo de resposta de cada tarefa que executa no sistema. Na segunda perspectiva, o problema é analisado considerando uma abordagem mais dinâmica. Uma abordagem multifase é apresentada para analisar a escalonabilidade das tarefas de tempo-real seguindo um modelo *fork-join* antes e durante o tempo de execução. Esta abordagem tem a particularidade de, durante o tempo de execução, utilizar o algoritmo de *work-stealing* para reduzir o tempo médio de resposta das tarefas de tempo-real.

O segundo problema (o problema da partilha de recursos em plataformas multiprocessador) é abordado considerando uma plataforma na qual o barramento é partilhado entre os vários núcleos e, por conseguinte, é uma fonte de interferência sempre que pedidos de memória são feitos em simultâneo pelos vários núcleos do sistema. Para resolver este problema, o modelo de 3 fases é utilizado. Em primeiro lugar, uma análise empírica é realizada para comparar o desempenho de diferentes políticas de atribuição de prioridades com uma implementação da política de escalonamento *global Earliest Deadline First* (EDF) que considera interferência entre tarefas. De seguida, um teste de escalonabilidade para o modelo de 3 fases é proposto, tendo em consideração a interferência no barramento e a interferência entre tarefas.

## **Abstract**

In the past, increasing the frequency in single-core processors was enough to accommodate new software features. However, due to physical limitations, processor manufacturers stopped releasing single-core processors in favour of multicore ones. While this move is beneficial for the software industry overall, as it allows the inclusion of more complex and demanding features into applications, the use of Commercial-Off-The-Shelf (COTS) multicore platforms in real-time systems still remains a challenge. In fact, in the real-time systems domain, predictability is considered more important than performance, and is a requirement for correctness in a domain well-known for their stringent timing requirements.

Two main reasons can be identified for such a challenge. First, COTS multicore architectures are designed for average-case performance and due to this, resources, such as memory components (*i.e.*, main memory, memory caches, *etc.*), peripheral devices, and buses, are shared among the different cores. Consequently, if care is not taken, timing deviations, from the ones estimated at design time, may occur due to interference whenever different cores simultaneously access shared resources. Second, the platform not only supports concurrent execution at a core level but it also supports parallel execution at the platform level. Therefore, the major goal for the real-time systems community is to find efficient ways of dealing with the inherent parallel behaviour of the platform, and at the same time, be able to ensure application predictability by taking into account the shared resources in the platform. In this dissertation, this goal is divided into two distinct problems which are dealt independently from each other: (i) the problem of scheduling parallel real-time tasks in multiprocessor platforms; and (ii) the problem of sharing resources in multiprocessor platforms.

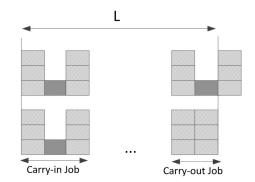

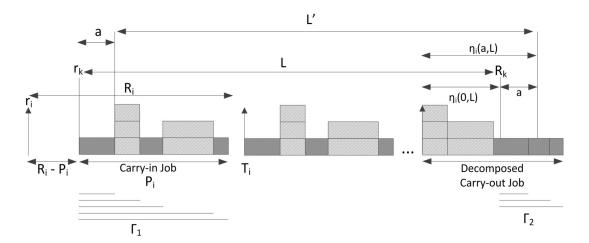

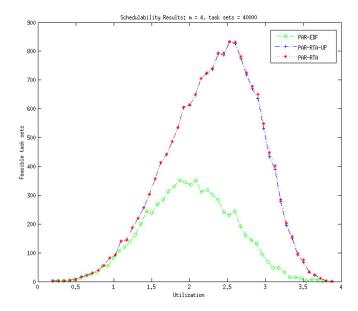

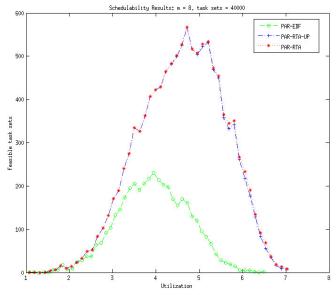

The first problem (scheduling parallel real-time tasks in multiprocessor platforms) is covered from two different perspectives. In the first one, we focus on the response-time of synchronous parallel real-time tasks. The model under consideration targets tasks with fixed priorities, composed of several segments, each with an arbitrary number of parallel and independent units of execution that can be executed in parallel. New concepts such as carry-out decomposition and sliding window are introduced to derive a worst-case scenario that allows one to compute the worst-case response-time of each task executing in the system. In the second perspective, the problem is analysed considering a more dynamic approach. A multi-stage approach is presented to analyse the schedulability of fork-join real-time tasks before and during runtime. The particularity of this approach is that during runtime the work-stealing algorithm is used to reduce the average response-time of real-time tasks.

The second problem (sharing resources in multiprocessor platforms) is addressed by considering a platform where the memory bus is shared among cores. Consequently, it is a source of interference whenever simultaneous memory requests are issued by the cores in the platform. To solve this problem, the 3-phase task model is used. First, an empirical analysis is performed where the performance of different priority assignment policies is compared against an implementation of the global Earliest Deadline First (EDF) scheduling policy that considers inter-task interfer-

ences. Then, a schedulability test for the 3-phase task model is derived by taking into account the bus interference and task interference.

## Acknowledgements

Many people contributed to this endeavour in many different ways. Thus, I would like to take this opportunity to show my respect and gratitude to all of them.

First of all, I am very grateful to my advisors, **Luís Miguel Pinho** and **Luís Miguel Nogueira**, for everything that they did for me. In the first place, for guiding me in the selection of a research topic and afterwards, for the time, support and long discussions about the research work that led to dissertation you are reading. In addition, for all the time and effort spent reviewing my work, including this dissertation. Finally, for teaching other valuable things related to life. Their friendship and professional collaboration meant a lot to me.

A PhD degree cannot be obtained without family support. For that, I have to thank my family in general, but specially my parents, **Carlos** and **Maria**, my wife **Joana** and our newborn **Dinis**, which also contributed to this research work in its own way, and finally, my brother **Luís and his family**.

To the people that collaborated with me, namely: **Marko Bertogna**, **Daniél Gracia Perez**, **Patrick Yomsi** and **Geoffrey Nellisen**. The hours we spent together discussing complex problems were very valuable to me. I learned several different things with all of you and I felt that not only I was improving as a researcher but also as a human being.

Finally, I would like to thank **CISTER Research Centre** as an institution for the opportunity and trust they gave me in order to pursue this degree. Moreover, as a research centre is just a hollow space without people, I also want to thank and give a warm appreciation to my co-workers at CISTER for sharing their insights, ideas, different visions and cultural perspectives, not only about my work but about life in general. A special thanks goes to **David Pereira**, **André Pedro** and **José Fonseca** for their friendship and support.

This research work was partially supported by National Funds through FCT (Portuguese Foundation for Science and Technology) and by ESF (European Social Fund) through POPH (Portuguese Human Potential Operational Program), under PhD grant SFRH / BD / 88834 / 2012.

Cláudio Maia

## **List of Publications**

The following publications were developed in the scope of the research activities presented in this dissertation.

#### **Journals**

Cláudio Maia, Patrick Meumeu Yomsi, Luís Nogueira, and Luis Miguel Pinho. Real-time semi-partitioned scheduling of fork-join tasks using work-stealing. *EURASIP Journal on Embedded Systems*, 2017(1):31, Sep 2017b. ISSN 1687-3963. doi: 10.1186/s13639-017-0079-5

## **Conferences (in chronological order)**

- Cláudio Maia, Luís Nogueira, and Luís Miguel Pinho. Supporting real-time parallel task models with work-stealing, March 2012. Research Poster at The Designing for Embedded Parallel Computing Platforms: Architectures, Design Tools, and Applications (DEPCP'2012) (DATE Workshop)

- Cláudio Maia, Luís Nogueira, Luís Miguel Pinho, and Marko Bertogna. Response-time analysis of fork/join tasks in multiprocessor systems. In *Proceedings of Work-in-Progress Session of the 25th Euromicro Conference on Real-Time Systems*, ECRTS '13, Paris, France, July 2013. Work in Progress Session

- Cláudio Maia, Marko Bertogna, Luís Nogueira, and Luis Miguel Pinho. Response-time analysis of synchronous parallel tasks in multiprocessor systems. In *Proceedings of the 22nd International Conference on Real-Time Networks and Systems*, RTNS '14, pages 3:3–3:12, New York, NY, USA, 2014. ACM. ISBN 978-1-4503-2727-5. doi: 10.1145/2659787.2659815

- Cláudio Maia, Patrick Meumeu Yomsi, Luís Nogueira, and Luis Miguel Pinho.

Semi-partitioned scheduling of fork-join tasks using work-stealing. In 2015 IEEE 13th International Conference on Embedded and Ubiquitous Computing, pages 25–34, Oct 2015. doi: 10.1109/EUC.2015.30

- Cláudio Maia, Luís Nogueira, Luis Miguel Pinho, and Daniel Gracia Pérez. A closer look into the aer model. In 2016 IEEE 21st International Conference on Emerging Technologies and Factory Automation (ETFA), pages 1–8, Sept 2016. doi: 10.1109/ETFA.2016.7733567

- Cláudio Maia, Geoffrey Nelissen, Luís Nogueira, Luis Miguel Pinho, and Daniel Gracia Pérez. Schedulability analysis for global fixed-priority scheduling of the 3-phase task model. In 2017 IEEE 23rd International Conference on Embedded and Real-Time

Computing Systems and Applications (RTCSA), pages 1–10, Aug 2017a. doi: 10.1109/RTCSA.2017.8046313

## **Contents**

| Re | esumo   |                                           | i   |

|----|---------|-------------------------------------------|-----|

| Al | bstrac  | rt                                        | iii |

| A  | cknow   | rledgements                               | v   |

| Li | st of I | Publications                              | ix  |

| 1  | Intr    | oduction                                  | 1   |

|    | 1.1     | Parallelism                               | 2   |

|    |         | 1.1.1 Example of an OpenMP Task           | 3   |

|    | 1.2     | Parallelism and Real-Time Systems         | 4   |

|    | 1.3     | Resource Sharing                          | 5   |

|    | 1.4     | Thesis Statement                          | 6   |

|    | 1.5     | Contributions                             | 7   |

|    | 1.6     | Thesis Structure                          | 8   |

| 2  | Bacl    | kground and Related Work                  | 9   |

|    | 2.1     | Task Characterisation                     | 9   |

|    | 2.2     | Platform Characterisation                 | 11  |

|    |         | 2.2.1 Processors                          | 12  |

|    |         | 2.2.2 Memory                              | 12  |

|    |         | 2.2.3 Memory Bus                          | 14  |

|    | 2.3     | Multiprocessor Scheduling                 | 17  |

|    | 2.4     | Parallel Real-Time Systems                | 19  |

|    |         | 2.4.1 Parallel Task Models                | 19  |

|    |         | 2.4.2 Earlier Parallel Models             | 20  |

|    |         | 2.4.3 Recent Parallel Models              | 21  |

| 3  | Sche    | edulability of Synchronous Parallel Tasks | 25  |

|    | 3.1     | Introduction                              | 25  |

|    | 3.2     | System Model                              | 26  |

|    | 3.3     | Critical Interference of Parallel Tasks   | 27  |

|    | 3.4     | Response-Time Analysis                    | 32  |

|    | 3.5     | Sliding Window Technique                  | 33  |

|    | 3.6     | Decomposing the Carry-out Job             | 34  |

|    | 3.7     | Workload of a Task Within a Window        | 35  |

|    | 3.8     | Schedulability Condition                  | 38  |

|    | 39      | Complexity                                | 39  |

xii CONTENTS

|    | 3.10         | Evaluation                                                                | 39        |  |  |  |

|----|--------------|---------------------------------------------------------------------------|-----------|--|--|--|

|    | 3.11 Summary |                                                                           |           |  |  |  |

|    | J.11         |                                                                           |           |  |  |  |

| 4  | Appl         | lying Work-stealing to Real-time Systems                                  | 43        |  |  |  |

|    | 4.1          | Introduction                                                              | 43        |  |  |  |

|    | 4.2          | Randomised Work-stealing                                                  | 44        |  |  |  |

|    | 4.3          | Limitations of Randomized Work-stealing with Respect to Real-Time Systems | 45        |  |  |  |

|    | 4.4          | Literature on Real-Time Work-Stealing                                     | 46        |  |  |  |

|    | 4.5          | A New Data Structure                                                      | 48        |  |  |  |

|    | 4.6          | Semi-partitioned Scheduling                                               | 49        |  |  |  |

|    | 4.7          | System Model                                                              | 50        |  |  |  |

|    | т. /         | 4.7.1 Earliest Deadline First                                             | 50        |  |  |  |

|    |              | 4.7.2 Multiframe Task Model                                               | 51        |  |  |  |

|    | 4.8          |                                                                           | 52        |  |  |  |

|    | 4.0          | Semi-partitioned Scheduling and Work-Stealing                             | 53        |  |  |  |

|    |              |                                                                           |           |  |  |  |

|    |              | 4.8.2 Offline Scheduling Phase                                            | 54        |  |  |  |

|    |              | 4.8.3 Online Scheduling Phase                                             | 55        |  |  |  |

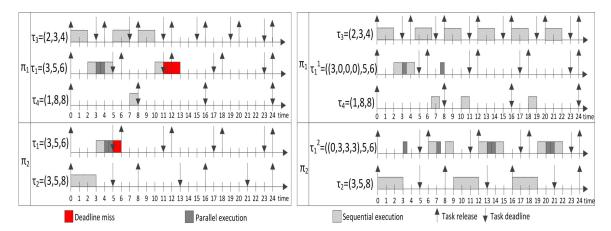

|    |              | 4.8.4 Example                                                             | 56        |  |  |  |

|    | 4.9          | Tasks with Density Greater Than 1                                         | 57        |  |  |  |

|    |              | Schedulability Analysis                                                   | 59        |  |  |  |

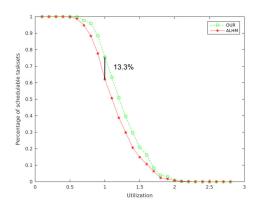

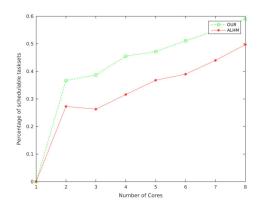

|    | 4.11         | Simulation Results                                                        | 63        |  |  |  |

|    |              | 4.11.1 Selected Heuristics                                                | 63        |  |  |  |

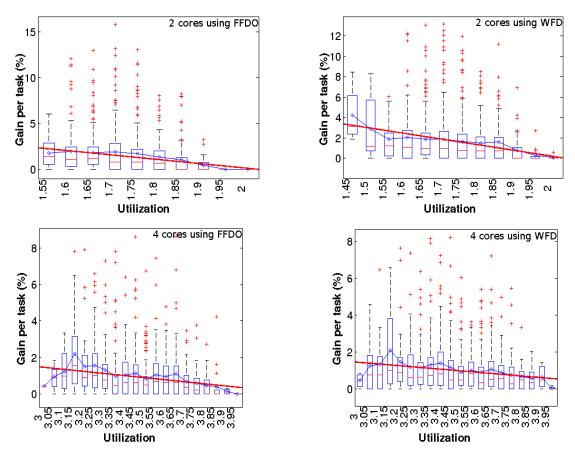

|    |              | 4.11.2 FFDO versus WFD                                                    | 64        |  |  |  |

|    |              | 4.11.3 Overheads of the Approach                                          | 68        |  |  |  |

|    | 4.12         | Summary                                                                   | 69        |  |  |  |

| _  | C - I        | July 1944 of the 2 Dhans Tools Madal                                      | 71        |  |  |  |

| 5  |              | dulability of the 3-Phase Task Model                                      | <b>71</b> |  |  |  |

|    | 5.1          | Introduction                                                              | 71        |  |  |  |

|    | 5.2          | System Model                                                              | 72        |  |  |  |

|    | 5.3          | Runtime Execution Model                                                   | 73        |  |  |  |

|    | 5.4          | 3-Phase vs. G-EDF in COTS Systems                                         | 73        |  |  |  |

|    |              | 5.4.1 Priority Assignment Policies                                        | 73        |  |  |  |

|    |              | 5.4.2 Simulator's Scheduling Behaviour                                    | 75        |  |  |  |

|    |              | 5.4.3 Experimental Settings                                               | 76        |  |  |  |

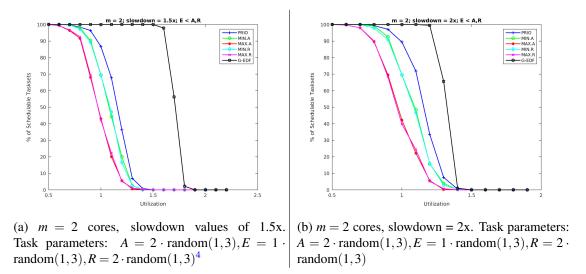

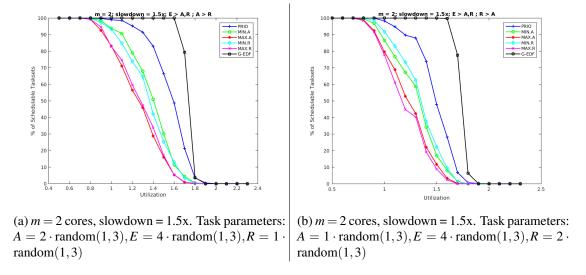

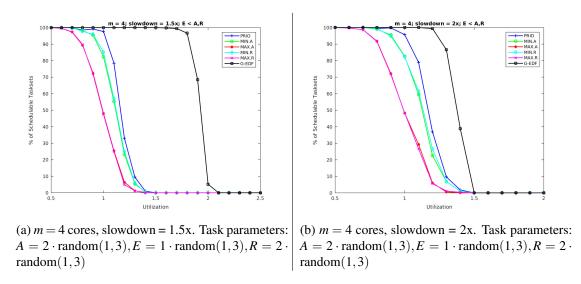

|    |              | 5.4.4 Experimental Results                                                | 77        |  |  |  |

|    | 5.5          | Global Fixed-Priority Scheduling of the 3-Phase Task Model                | 82        |  |  |  |

|    |              | 5.5.1 Scheduling Policy                                                   | 82        |  |  |  |

|    |              | 5.5.2 Background                                                          | 84        |  |  |  |

|    |              | 5.5.3 A Different Perspective                                             | 87        |  |  |  |

|    |              | 5.5.4 Schedulability Analysis                                             | 89        |  |  |  |

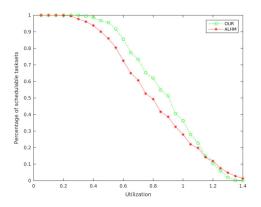

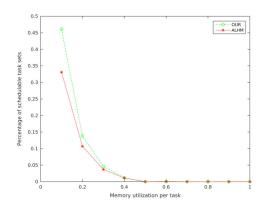

|    |              | 5.5.5 Experimental Results                                                | 95        |  |  |  |

|    | 5.6          | Summary                                                                   | 97        |  |  |  |

|    |              | •                                                                         | -         |  |  |  |

| 6  | Conc         | clusion                                                                   | 99        |  |  |  |

|    | 6.1          | Future Work                                                               | 101       |  |  |  |

| Re | feren        | ces                                                                       | 103       |  |  |  |

# **List of Figures**

| 1.1  | Graphical representation of the code presented in Listing 1.1                            |

|------|------------------------------------------------------------------------------------------|

| 2.1  | Memory hierarchy in current COTS platforms                                               |

| 2.2  | Example of a 3-phase task model schedule                                                 |

| 2.3  | Example of a fork/join task $\tau_i$                                                     |

| 2.4  | Example of a synchronous parallel task $\tau_i$                                          |

| 3.1  | Task $\tau_i$ interfering on task $\tau_k$                                               |

| 3.2  | Densest possible packing of threads within the problem window                            |

| 3.3  | Densest possible packing of threads when a task skips some segment                       |

| 3.4  | Example of a decomposed job                                                              |

| 3.5  | Response-time analysis details                                                           |

| 3.6  | Number of schedulable task sets detected by the considered tests for $m = 4 \dots$       |

| 3.7  | Number of schedulable task sets detected by the considered tests for $m=8$               |

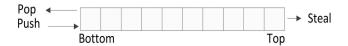

| 4.1  | Work-stealing deque data structure                                                       |

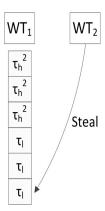

| 4.2  | Priority inversion scenario                                                              |

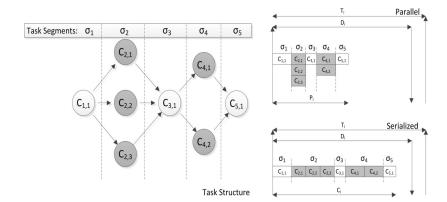

| 4.3  | Fork-join task                                                                           |

| 4.4  | Illustrative example of the proposed approach                                            |

| 4.5  | Task decomposition with one task                                                         |

| 4.6  | Result of applying the proposed approach to a task set that contains a task with         |

|      | density greater than 1                                                                   |

| 4.7  | Analysis proposed by Dorin et al. in [Dorin et al., 2010]                                |

| 4.8  | Result after the offline analysis                                                        |

| 4.9  | Example of work-stealing and intermediate deadline computation                           |

|      | Possible cases for the admission control test                                            |

| 4.11 | Percentage of unallocated tasks                                                          |

| 4.12 | Comparison between FFDO and WFD                                                          |

| 4.13 | Simulation results for FFDO and WFD                                                      |

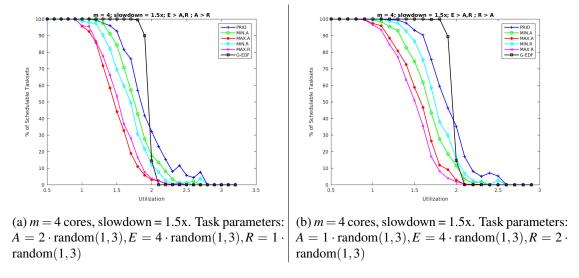

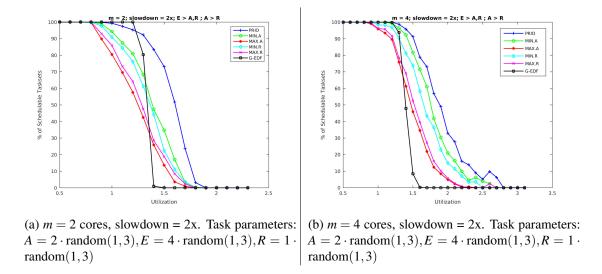

| 5.1  | Simulation results for $m = 2$ , $E$ -phase smaller than $A$ and $R$ -phases             |

| 5.2  | Simulation results for $m = 2$ , $E$ -phase larger than both $A$ and $R$ -phases         |

| 5.3  | Simulation results for $m = 4$ , $E$ -phase smaller than $A$ and $R$ -phases             |

| 5.4  | Simulation results for $m = 4$ , $E$ -phase larger than both $A$ and $R$ -phases         |

| 5.5  | Comparison between $m = 2$ and $m = 4$ , $E$ -phase larger than both $A$ and $R$ -phases |

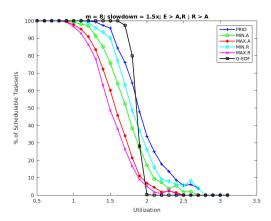

| 5.6  | Simulation results for $m = 8$ cores, slowdown = 1.5x                                    |

| 5.7  | Problem Window                                                                           |

| 5.8  | Computing the overlap lower-bound for $\rho = 2, m = 3$ in [Alhammad and Pelliz-         |

|      | zoni, 2014]                                                                              |

xiv LIST OF FIGURES

| 5.9  | Pessimism of the analysis in [Alhammad and Pellizzoni, 2014]              |   |  |   | 87 |

|------|---------------------------------------------------------------------------|---|--|---|----|

| 5.10 | Our schedulability analysis approach                                      |   |  |   | 88 |

| 5.11 | Computing an upper-bound on bus holes                                     |   |  |   | 92 |

| 5.12 | Bus holes                                                                 |   |  |   | 93 |

| 5.13 | Schedulability ratio for $m = 4$ and as a function of the number of cores |   |  |   | 95 |

| 5.14 | Schedulability ratio for $m = 2$ and as a function of the memory ratio    | _ |  | _ | 96 |

## Acronyms

BFD Best-fit Decreasing

COTS Commercial Off-the-shelf

CPU Central Processing Unit

DAG Directed Acyclic Graph

DBF Demand Bound Function

DRAM Dynamic Random Access Memory

EDF Earliest Deadline First

FFD First-fit Decreasing

FCFS First Come, First Serve

FIFO First-In, First-Out

GMF Generalized Multiframe model

LIFO Last-In, First-Out

MPI Message Passing Interface

POSIX Portable Operating System Interface

RAM Random Access Memory

TDMA Time-division Multiple Access

WCET Worst-case Execution Time

WFD Worst-fit Decreasing

## **Chapter 1**

## Introduction

The multiprocessor trend restarted recently (first multiprocessor systems appeared in the 60s/70s) and is moving at a fast pace. In 2001, Sun Microsystems and IBM (in a separated effort) manufactured the dual-core processors. Later on, in 2006, this type of processors became a mainstream technology powered by Intel and AMD. This shift in paradigm (moving from uniprocessor to multiprocessor systems) occurred due to the physical limitations of computer chips. Increasing the operating frequency and voltage of the chips leads to an exponential increase in power consumption and heat dissipation issues. In order to overcome such physical limitations, chip manufacturers increased the number of computing units operating in parallel per single chip, while maintaining a lower frequency of operation, i.e., multicore systems. As a result of this paradigm shift, computing systems are gradually becoming multiprocessor, with each chip being composed of multiple core units. Nowadays, different platforms present a varying number of cores per chip, ranging from the tenths up to the hundreds. Some notable examples of such platforms are TILE64 from Tilera [Bell et al., 2008], the Epiphany processors designed by Adapteva [Adapteva, 2014] and the MPPA-256 Manycore Processor developed by Kalray [de Dinechin et al., 2013]. Future generations of processors are expected to integrate thousands of simple processors in a single chip [Asanovic et al.,  $20061.^{1}$

Perhaps the advantage of multicore systems that immediately stands out is the opportunity they offer to increase application performance by allowing each application to execute its code simultaneously and in parallel. However, while sequential programs execute faster if the clock speed of the processors is increased (under the assumption that concurrency is neglected), this is not the case for multicore platforms due to certain restrictions, such as workload distribution, synchronisation and coordination operations frequently occurring between cores, and the existence of shared resources. Hence, to obtain the best efficiency possible and take complete advantage of these platforms, sequential programs need to be rewritten and such restrictions be taken into account. This aspect is specially relevant in the real-time systems domain, the domain covered in this dissertation, where predictability is of utmost importance. In this domain and for efficiency

<sup>&</sup>lt;sup>1</sup>In this dissertation, the terms multicore and multiprocessor are used interchangeably. Nevertheless, a clarification for the difference that exists between a core and a processor is given in the next chapter.

2 Introduction

purposes, the move to a multiprocessor centred paradigm imposes new challenges as it requires moving out from traditional multiprocessor scheduling<sup>2</sup> algorithms that are focused on sequential tasks to scheduling algorithms that contemplate parallel tasks.

In this chapter we start by introducing relevant concepts related to parallelism and provide an example of how it can be exploited by applications, in Section 1.1. Then, we focus on the challenge of exploiting parallelism in real-time systems and the problem of resource sharing introduced by multiprocessor platforms, in Section 1.2 and Section 1.3, respectively. With both of these in mind (parallelism and resource sharing), we explicitly state which problems this dissertation intends to solve, in Section 1.4, and its contributions, in Section 1.5. Finally, the thesis structure is presented in Section 1.6.

#### 1.1 Parallelism

Parallelism in computer programs can be exploited either explicitly, by using explicit parallel programming languages, or implicitly, by using implicit parallel programming languages [Freeh, 1996].

An explicit parallel programming language provides special constructs that allow the programmer to identify the opportunities for parallelism and break the program by its logical functionality. This division by functionality results in units of execution (commonly known as tasks or threads) that may be simultaneously executed in parallel in each of the platform's cores. The advantage of using such approach is that the programmer can write very efficient code at the cost of the time needed to produce it.

By using an implicit parallel programming language, the programmer relies on the compiler to automatically manage and extract parallelism at compile time in an implicit manner. The disadvantage of this approach is that it is compiler dependent and therefore not all parallelism may be discovered.

Besides the type of programming languages, as described above, there are other important aspects that require special attention from the programmer when developing parallel applications, as for instance the selection of programming models and frameworks/libraries.

Two well-known programming models [Diaz et al., 2012] exist for the development of parallel applications - shared memory and distributed memory models. In the shared memory model, all processors have access to the same random access memory (RAM) and tasks exchange data by accessing the shared memory. In the distributed memory model, each processor has access to its own private memory. If by any means a task needs data residing in another's processor memory, then both processors need to communicate by exchanging messages via a communication channel.

Several existing frameworks/libraries support the aforementioned models of computation (*e.g.*, OpenMP [OpenMP, 2011] or POSIX threads [Gallmeister, 1995] for shared memory, and Message Passing Interface (MPI) [MPI, 2014] for distributed memory, to name a few). The goal of

<sup>&</sup>lt;sup>2</sup>The decision process that deals with the allocation of workload to system resources and its sequencing over a period of time is known as scheduling.

1.1 Parallelism 3

Listing 1.1: Simple OpenMP Example

```

some initialisation code

#pragma omp parallel num_threads(4)

{

... some computing intensive parallel code ...

}

clean up code

```

such frameworks/libraries is to enhance the programming languages and runtime environments with specific features that allow a programmer to focus on the functionality of a computer program, instead of focusing on the specific details of parallelisation. Some of these features include mechanisms for task creation and destruction, task synchronisation and scheduling, among others. Thus, a big advantage of such parallel frameworks/libraries is that they ease the programmer's effort by reducing the complexity of developing parallel programs.

#### 1.1.1 Example of an OpenMP Task

Due to its importance and dominance in traditional multicore architectures, where all cores have access to the same memory address space, let us focus on the shared memory model and more specifically on OpenMP. Using OpenMP, a programmer has full control over the code parallelisation, thus making it an explicit parallel programming framework/library. Hence, programmers can annotate their programs to expose opportunities for parallelism and suggest a possible parallel decomposition to the framework's runtime. The annotations act as hints for parallelisation which may be considered by the runtime environment, as a function of the system load and with the objective of exploiting the maximum amount of parallelism possible.

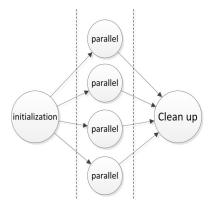

Listing 1.1 presents a simple OpenMP example to show the reader of how such frameworks/libraries operate. In the example, the main thread of execution sequentially executes some initialisation code. After completing the initialisation phase, the main thread requires from the runtime the creation of 4 threads. Each of threads is responsible for the execution of the parallel block defined within the pragma *omp parallel*. After completing their execution, each of the parallel threads synchronise with the main thread so that the clean up code is executed. Then, the program ends its execution.

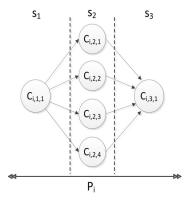

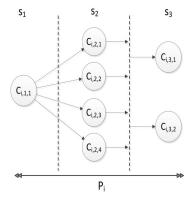

This model of execution is known as the *fork-join* model due to the fact that the main thread forks into several threads that join into a single main thread at the end of their execution. Figure 1.1 depicts a graphical representation of the code in Listing 1.1.

4 Introduction

Figure 1.1: Graphical representation of the code presented in Listing 1.1

## 1.2 Parallelism and Real-Time Systems

A common definition found in the literature defines a real-time system as a system where its correct behaviour not only depends on the logical correctness of the system, but also on the time at which the operations are performed [Stankovic, 1988]. This type of systems is known for their predictability and stringent design requirements [Durrieu et al., 2014b; Leteinturier, 2007; Monot et al., 2010]. While in the past these systems were targeted at control applications, which are marked by their limited processing, a new set of applications (ranging from smart grids to autonomous driving) is demanding high processing in conjunction with real-time performance, and thus, powerful hardware is required to satisfy their needs [Pinho et al., 2015]. In fact, the required computing capacity they need can be obtained from state of the art multiprocessor platforms. In particular, real-time systems may take advantage of the platform's parallelism by distributing workload among the different cores for simultaneous execution, while using efficient scheduling techniques and consequently, better manage system resources.

However, bringing parallelism into real-time systems is not an easy task. Specially when the scheduling of applications is considered. Liu and Layland [Liu and Layland, 1973] observed the complexity of multiprocessor scheduling by stating the following:

"... bringing in additional processors adds a new dimension to the scheduling problem. The simple fact that a task can use only one processor even when several processors are free at the same time adds a surprising amount of difficulty to the scheduling of multiple processors."

While the uniprocessor scheduling problem reduces to deciding *when* to schedule each task, a new dimension adds to this one when shifting to multicores as it must also be decided *where* to execute each task.

Traditional multiprocessor scheduling deals with the scheduling of sequential tasks, that is, tasks which can only run in a single core. With this type of tasks, parallelism can only be exploited by increasing the number of tasks executing in the system and increasing the number of cores does not increase the execution speed for each task. This model of execution is known as

inter-task parallelism. Most results in real-time scheduling are devoted to the study of sequential tasks executing on multiple processors (see [Davis and Burns, 2011a] for a comprehensive and upto-date survey). However, the shift from uniprocessors to multiprocessors revealed that scheduling real-time tasks is no longer a problem of scheduling sequential tasks. A real-time task may now exploit intra-task parallelism and be split into a set of sub-tasks that can be executed simultaneously in different processors at the same time instant (*i.e.*, potentially overlapping in time). Such a task is commonly denoted as a parallel real-time task or in short a parallel task.

On one hand, it is possible to take advantage of available cores to improve the execution of complex tasks with tighter timing constraints, whenever there is an opportunity in the system for the parallel execution of sub-tasks. On the other hand, such an approach requires efficiency from the system scheduler as now there is the need to map individual sub-tasks to each of the available cores. If the task's parallelism is rather regular, then it may be possible to find a mapping of tasks to cores at design time, such that the workload is balanced and the overall execution time of the task is reduced. But if the task's parallelism is irregular, then a static assignment of sub-tasks to cores may produce sub-optimal schedules where the workload is imbalanced (that is, some cores are excessively loaded while others are lightly loaded or even idle). Thus, the system scheduler must be efficient and capable of dynamically balance the workloads during runtime by taking into account the current system state and the dynamic nature of the tasks. The introduction of dynamic load balancing algorithms in the real-time systems domain is rather challenging due to the difficulty in guaranteeing the predictability of the system under analysis.

In the recent literature of real-time systems it is possible to find a few works that tackle parallel real-time tasks. Some of these works, namely [Lakshmanan et al., 2010] and [Saifullah et al., 2011], assume a model of execution similar to the fork-join model presented above in Figure 1.1. Nevertheless, analysing models that can leverage parallelism can be challenging from a schedulability viewpoint. For instance, usually there exists an execution dependency between different task segments <sup>3</sup> which imposes a partial order on execution.

## 1.3 Resource Sharing

In current multiprocessor architectures cores are not independent entities. They share physical resources, such as memory buses, memory controllers, last level caches, *etc.*, among themselves. While sharing resources may be beneficial for the threads of the same application, it may not be for threads of distinct applications as they compete for the resources, thereby introducing a problem of predictability for the real-time systems domain. In order to understand the implications of this problem, the reader needs to first understand how real-time systems are analysed with respect to their timing properties.

An important restriction that underpins the design of real-time systems is that (desirably) all timing properties should be met under all possible conditions. Consequently, these systems are

<sup>&</sup>lt;sup>3</sup>A segment of a parallel real-time task is a region that is composed of an arbitrary number of sub-tasks where all sub-tasks can execute in parallel and independently from sub-tasks in other segments

6 Introduction

analysed taking into account worst-case scenarios by the means of a *schedulability analysis*. The outcome of such analysis is a yes or no answer stating whether the system meets its deadlines or not, or in other words, whether it is schedulable or not.

An important parameter used in the definition of real-time applications and in the schedula-bility analysis is the *worst-case execution time* (WCET). The WCET is an upper-bound on the application's execution time considering the maximum time that it takes to execute in isolation in a given hardware platform<sup>4</sup>. WCET is also the parameter that is affected during runtime whenever there is contention in the system. Specifically, when two (or more) applications executing in two (or more) cores access shared resources simultaneously, the application's WCET may increase, which may jeopardize the results obtained offline from schedulability analysis.

Contention may occur due to several reasons, for instance a shared resource may only admit one access at a time (as it typically occurs in buses) or the state of a resource may be modified by one application accessing it in a way that it affects a concurrent application, causing a slowdown to the latter application (this behaviour is typically seen in shared caches) [Abel et al., 2013].

Several studies, as for instance [Zhuravlev et al., 2010], [Nowotsch and Paulitsch, 2012], [Radojković et al., 2012], show that due to shared resource contention, the execution times of applications may vary significantly. In particular, a common observed effect is the slowdown of applications due to *co-running applications*, *i.e.*, applications running on cores that share a resource. As an example on the amount of slowdown that can be observed due to shared resource contention, the authors in [Nowotsch and Paulitsch, 2012] observed a maximum slowdown of 5.1x in application execution, compared to execution in isolation, when multiple cores access network and memory concurrently. An even higher slowdown was observed by the authors in [Nélis et al., 2016]. In their research, they observed a slowdown of 8x due to co-running applications.

Solutions exist for the problem of contention in shared resources. For the cache contention problem, existing solutions apply cache partitioning strategies to eliminate interference between tasks from different cores, and consequently, bound the interference in the resulting non-partitioned shared caches. For the problem of bus contention, existing solutions use protocols to arbitrate the access to shared resources and analyse them accordingly in order to derive safe bounds. Such protocols can be time driven, *e.g.*, Time-division Multiple Access protocol (TDMA); event driven, *e.g.*, First Come, First Serve, Round Robin, *etc.*,; or a mix of both [Abel et al., 2013].

The conclusion that must be drawn from the above results is that special care must be taken when executing real-time applications in multicore platforms due to the existence of shared resources.

#### 1.4 Thesis Statement

Moving from uniprocessor systems to multiprocessor systems is likely to fail if one does not take into account the problems that arise from such evolution, as the ones described above. Treating applications as if they are executing in a uniprocessor system while ignoring the parallel nature

<sup>&</sup>lt;sup>4</sup>WCET and other parameters are formally described in the next chapter.

1.5 Contributions 7

of the platform leads to an underutilization of system resources on one hand, and on the other hand, to an increase in interference due to co-running tasks. A clear aspect that still needs to be addressed by the real-time systems community is the lack of efficient models to handle the execution of parallel real-time applications and, ideally, that also cover the problem of resource sharing. Thus, the end goal of this dissertation is to have new models or enhance existing ones in order to derive the sound schedulability analysis that is needed by real-time applications running in multiprocessor systems.

This dissertation addresses the following two problems:

- 1. Problem of scheduling parallel real-time tasks in multiprocessor systems;

- 2. Problem of resource sharing in multiprocessor systems.

In particular, and related to each general problem above, we want to answer the following questions:

- 1. Is it possible to compute response-time upper bounds for parallel tasks when executing in multiprocessor systems?

- 2. Considering a scenario with co-running tasks and a shared resource, is it possible to compute upper-bounds on the interference imposed by co-running tasks in a multiprocessor system?

Motivated by the problems and questions above, the central proposition of this thesis is the following:

Real-time systems can be provided efficient schedulability tests that allows one to take advantage of multiprocessor systems. Supported models can consider intra-task parallelism or inter-task parallelism with shared resources. When dealing with intra-task parallelism, load-balancing is considered either naturally or via work-stealing. When dealing with shared resources, a model that decouples memory accesses from execution is effective when compared to other models that do not take shared resources into account.

#### 1.5 Contributions

Considering the problems and questions above, this research work proposes the following contributions. For the first problem and first question, two contributions are proposed. The first contribution, presented in Chapter 3, considers a parallel task model that generalises the fork-join model presented above, known as the synchronous task model. Under this model, the worst-case scenario is derived in order to compute the worst-case response-time bounds for multiprocessor systems composed of identical processors. The second contribution, presented in Chapter 4, takes advantage of work-stealing [Blumofe and Leiserson, 1999] to reduce the average response-time of real-time tasks in order to create additional room in the schedule for less-critical tasks. The presented approach is a multi-stage approach that analyses the schedulability of the real-time tasks before and during runtime.

8 Introduction

For the second problem and second question, the contribution proposed, presented in Chapter 5, uses a task model known as the 3-phase task model. In this model, memory accesses are decoupled from execution in order to circumvent the uncontrolled sources of interference, occurring due to co-running tasks in multiprocessor systems. An empirical analysis is carried first to compare the performance of different priority assignment policies against an implementation of global Earliest Deadline First (EDF) scheduling policy that considers inter-task interferences. Then, a schedulability test for the 3-phase task model is derived using a different analysis perspective. Instead of analysing the system following the standard's core's perspective, a bus perspective is used.

#### 1.6 Thesis Structure

The remainder of this dissertation is structured as follows:

Chapter 2 details the most important properties about the platform and real-time tasks that are relevant for this dissertation. Moreover, it reviews the most important results found in the literature regarding the problem of scheduling parallel real-time tasks and the problem of memory bus contention.

Chapter 3 presents the schedulability analysis of fixed-priority synchronous parallel tasks executing in homogeneous multiprocessor systems.

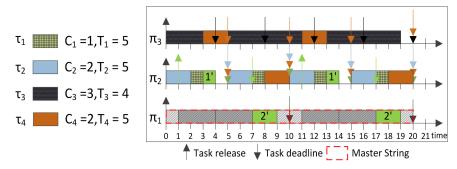

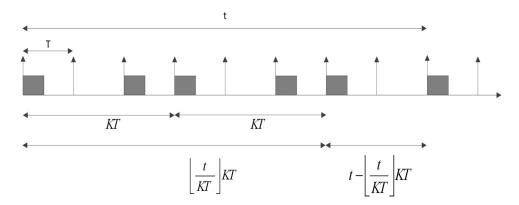

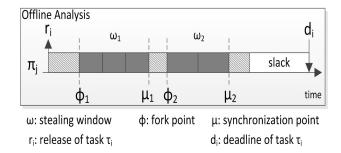

Chapter 4 presents an approach that takes advantage of the work-stealing algorithm in a semi-partitioned scheduling setting for scheduling fork-join tasks. The proposed approach is a multi-stage approach that consists of an offline stage and an online stage. During the offline stage, tasks are mapped to cores so as to fill the capacity of the cores as much as possible. During the online stage, a variant of work-stealing is used among cores to balance the workload and consequently, to reduce, whenever possible, the response-time of the tasks that were accepted offline. The schedulability analysis for the approach is presented as well as the experimental results showing its viability.

Chapter 5 is focused on the problem of memory bus contention in real-time systems. It presents an empirical study that compares the performance of different priority assignment policies considering the 3-phase task model. Then, a schedulability test for the 3-phase task model is derived considering an approach that analyses the system from a bus perspective instead of following the common core's perspective. Results show that memory bus contention is a relevant problem in current multiprocessor platforms and that the 3-phase task model is a viable model to circumvent it.

Chapter 6 completes this dissertation by presenting some concluding remarks about the research work presented in this manuscript and outlining future work.

## Chapter 2

## **Background and Related Work**

A real-time system is designed (in its simpler form) to capture events from the environment using sensors and respond to those events in a timely manner through actuators (*i.e.*, in a generic sense, we denote the system that is being monitored and controlled as *controlled system*). In the context of real-time systems, timely manner means before a *deadline*, which is the maximum time within which a response must be produced. In these systems, the response time of the system, that is (in a non-formal manner) the time that it takes to fully respond to an input event or stimulus, is an important metric to consider as its performance may be affected depending on how long it takes to respond to the stimulus. In some cases, if the response time takes more time than the one expected at design time, catastrophic consequences may occur.

This chapter covers the main concepts related to the theory of real-time systems. It starts by characterising real-time tasks in Section 2.1, followed by the characterisation of the platform in Section 2.2. Concerning the platform, the main components are covered, namely the processors, the memory and the memory bus. Next, as scheduling is used throughout this dissertation, we devote our attention to multiprocessor scheduling theory in Section 2.3 to convey the concepts needed for the reader in order to understand the contributions of this dissertation. Finally, as this dissertation is also partly focused on the scheduling of parallel real-time tasks, we present in Section 2.4 the most relevant properties of parallel real-time systems.

#### 2.1 Task Characterisation

A real-time application is modelled as a set of *tasks*, commonly denoted as  $\tau$ . Each task  $\tau_i$  in the set  $\tau$  has functional and timing requirements (among other non-functional requirements) that must be guaranteed during runtime so that the result of its execution is deemed correct.

A real-time task can be classified as *hard*, *firm* or *soft*, according to the time instant at which its response should be completed. If a response to an event should always occur within a time period no greater than its deadline, then the task is classified as a *hard* real-time task. In this case, having a result after the deadline may cause catastrophic consequences for the controlled system. Hard real-time tasks should be guaranteed before the execution of the system, by using

offline schedulability analysis techniques. A task is classified as *firm* if producing a response to an event after the deadline is useless for the controlled system. In this case no serious consequences may result from the deadline miss. Finally, a task is classified as a *soft* real-time task if deadline misses are tolerated, as long as they are bounded. For this latter case, in case a deadline miss occurs, the output value still presents some utility for the system, however the controlled system suffers a performance degradation. Both firm and soft real-time tasks can be guaranteed by using schedulability analysis techniques that can be applied during the execution of the system.

Each new release of a task is denoted as a *job* meaning that a new instance of such task is being released into the system for execution. Tasks may have different release patterns, according to the frequency at which they are released into the system. Thus, tasks can be classified as *periodic*, *sporadic* or *aperiodic*.

A task that has periodic releases is denoted as a *periodic* task. Periodic tasks are characterized by a *period*, usually denoted as  $T_i$ , which indicates the frequency of release of each of its jobs. It is a common assumption found in the literature that during runtime a periodic task may release a potentially infinite sequence of jobs, where each job is released  $T_i$  time units apart from each other. In a *sporadic* task, the release of each of its jobs is separated by a *minimum inter-arrival interval*, also denoted as  $T_i$ . The interpretation for this parameter is that consecutive jobs of a sporadic task are *at least* separated  $T_i$  time units apart from each other. Nevertheless, at runtime the frequency of release may be larger than  $T_i$ . Similarly, as it happens to periodic tasks, the number of jobs released by sporadic tasks may potentially be infinite. Finally, in *aperiodic* tasks, task releases do not follow a well-known pattern and therefore do not have a period or a minimum inter-arrival time.

If all tasks in the set  $\tau$  are released in the system at the same time instant, then the tasks' release is denoted as *synchronous*. On the other hand, if tasks are released at different time instants (*e.g.*, separated by some time offset), then the tasks' release is denoted as *asynchronous*.

Besides the period, there are two other important parameters that are used in the definition of real-time tasks, namely the worst-case execution time and deadline.

Several aspects influence the execution time of a task, as for instance its inputs, the scheduling algorithm, the platform, among others. The impact of these aspects during each task's execution can be observed in the duration of each of its jobs, that is, different jobs may have different execution times. Thus, in order to keep the system predictable throughout its execution, the *worst-case execution time* (WCET), denoted as  $C_i$ , is used. The task's WCET is an upper-bound on the time that it takes to execute the task in isolation in a given hardware platform.

The *deadline*, usually denoted as  $(D_i)$ , represents the time instant at which the job of a task must complete its execution. Tasks can be further characterized according to the relation that exists between the deadline and the period. A task has a *constrained deadline* when its deadline is no greater than the period  $(D_i \le T_i)$ . A special case of constrained deadline tasks is known as *implicit* deadline tasks and occurs when the task's deadline equals its period  $(D_i = T_i)$ . Finally, a task is

said to have an arbitrary deadline if there is no restriction on the value of the deadline  $D_{i}$ .

Two other task properties can be defined, namely *utilization* and *density*. The *utilization* of task  $\tau_i$ , denoted as  $U_i$ , is defined as  $U_i = \frac{C_i}{T_i}$ . The task's utilization represents the percentage of time the task is allocated to a given processor by executing  $C_i$  time units every  $T_i$  time units. The *density* of task  $\tau_i$ , denoted as  $\lambda_i$ , is defined as  $\lambda_i = \frac{C_i}{\min(D_i, T_i)}$ . The task's density represents the percentage of time the task is allocated to a given processor by executing  $C_i$  time units every  $D_i$  time units. While for implicit deadline task sets the density equals the utilization of the task, for constrained deadline task sets the result is different. These two properties can be also defined for task sets. Thus, the *total utilization* of a set of n tasks  $\tau$  is defined as  $U_{\tau} \stackrel{\text{def}}{=} \sum_{i=1}^n U_i$ . The total utilization of a task set represents the percentage of time the processor is allocated for the execution of the n tasks given that each task executes for  $C_i$  time units every  $T_i$  time units. Therefore, it indicates the minimum capacity that the platform must provide in order to execute the task set  $\tau$ . The *total density* of a set of n tasks  $\tau$  is defined as  $\lambda_{\tau} \stackrel{\text{def}}{=} \sum_{i=1}^n \lambda_i$ .

A task set  $\tau$  is said to be *feasible* if there exists some scheduling algorithm that can schedule all possible job sequences released by the tasks belonging to  $\tau$ , without missing any of the task's deadlines. A *feasibility test* determines if the task set  $\tau$  executing on a given platform  $\Pi$  is feasible on that platform.

A task is said to be *schedulable*, with respect to a given scheduling algorithm, if it completes execution before its deadline when scheduled using that scheduling algorithm. In other words, the scheduling algorithm guarantees that the worst-case response time of the task is no greater than its deadline. The schedulability of task sets with respect to a scheduling algorithm and a platform can be evaluated through a *schedulability test*. That is, a *schedulability test* determines if a task set  $\tau$  scheduled using a scheduling algorithm S in a given platform  $\Pi$  is schedulable using S on  $\Pi$ .

A schedulability test can be *sufficient*, *necessary* or *exact*. A *sufficient* test implies that if the test is passed, then the task set is schedulable, however if the test is not satisfied then the task set under evaluation may be schedulable or not. Nothing can be concluded from the test and another test shall be used. A *necessary* test entails that if the test is passed, then the task set may be schedulable but not necessarily. However, if the test is not passed, then the task set is certainly not schedulable. An *exact* test is both necessary and sufficient.

### 2.2 Platform Characterisation

In this section, the most important hardware components are described, *i.e.*, the ones that have influence in this dissertation's contributions and somehow, the ones that have the most impact in the execution of a real-time task. We start by introducing the notion of processor, core and multiprocessor system, the memory, and finally, we discuss the influence that the memory bus has in the execution of real-time systems.

<sup>&</sup>lt;sup>1</sup>Without loss of generality, in this dissertation all time intervals and task parameters are assumed to be integer multiples of the system clock.

#### 2.2.1 Processors

Several terms are used as synonyms for the central processing unit (CPU) in a computing system, as for instance processor or core, sometimes causing confusion. Specially when these terms are generalized to include multiple processing units, such as multiprocessors or multicores. Thus, in order to avoid confusion we clarify each of these terms in this section.

Originally, the CPU was a processor chip made of millions of transistors containing a single processing unit and a few other units to perform several operations (*e.g.*, arithmetic, logic, *etc.*). Consequently, the term processor is used as a synonym for CPU.

In a multiprocessor system, the platform contains several CPUs, each in a physical chip. However, with the advent of multicore systems, each chip started to include more than one processing unit *per* chip. Thus, in this configuration, each processing unit is denoted as a *core*. As it was explained in the introductory chapter, the reason for such a paradigm shift had to do with the physical limitations of chips. Hence, the industry opted to increase the parallelism provided in a single chip by the inclusion of several cores instead of increasing the processing speed of each processing unit (in a single chip).

In this dissertation, the term processor and core are used interchangeably and as a synonym for a single processing unit in the system.

Multiprocessor systems can be classified into three classes according to the characteristics of the processors present in the platform. If each processor in the platform presents the same computing capacity, *i.e.*, meaning that the frequency is equal in all processors, then the platform is said to have *identical* or *homogeneous* processors (as for instance [Bell et al., 2008] and [Adapteva, 2014]). In this class, all processors are interchangeable as a task takes the same amount of time to complete its WCET (in isolation) in every processor. If different processors in the platform have different computing capacities, the platform is said to be composed of *uniform* or *related* processors. In this case the rate of execution of a task depends on the frequency of the processor in which it executes. Finally, there is the *heterogeneous* or *unrelated* processor class. In this class, processors are different among themselves and consequently, the execution time of the tasks may differ between processors and some tasks may not be able to execute in all/some processors. An example of a platform belonging to this class is the MPPA-256 Manycore Processor developed by Kalray [de Dinechin et al., 2013].

In this dissertation we only consider identical multiprocessor platforms.

#### **2.2.2 Memory**

In the past years dynamic random access memory (DRAM) speed did not increase in the same proportion as CPU speed. In fact, the achieved improvement is much less than the one observed in the CPU. The difference in speed between both components leads to a speed gap that eventually causes memory accesses (even in those cases where a program is composed of only a few memory instructions) to dominate the total time spent executing a program. This phenomenon was predicted in [Wulf and McKee, 1995] and is known as the *memory wall*.

13

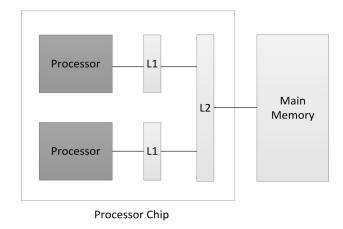

Figure 2.1: Memory hierarchy in current COTS platforms

In order to overcome the limitations of such a small increase in memory speed and at the same time attempt to decrease the memory access latencies, a hierarchical approach is used in modern computing systems.

The memory hierarchy is organized in several levels where each level is smaller in size and faster than the subsequent level in the hierarchy (when moving away from the processor chip). The faster memories that are closer to the processor are denoted as *caches* and, usually, are located within the processor chip. Caches act as a buffer for the data residing in main memory<sup>2</sup> and work according to the principle of locality which states that programs are likely to reuse data and instructions they have used recently.

Let us use Figure 2.1 to explain the reader how data traverses the memory hierarchy. The hierarchy in the figure has 3 levels, cache L1 (private to the core connected to it), cache L2 (shared between the cores connected to it) and finally, main memory (shared by all cores in the system). In our example, we assume a task is running in a single processor and it does not migrate to the other processor. When executing a task, the processor looks first for program data/instructions in cache L1. If data/instructions are found in that cache then there is a *cache hit* and the processor can use them without requesting data/instructions from the other levels. Otherwise, a *cache miss* occurs (data/instructions are not in the cache) and a request is made to the subsequent level. In our example, that level is L2. Then, the process is repeated. A hit or a miss may occur. If a hit occurs data is moved to level L1, otherwise a data request is made to main memory in order to be retrieved and stored temporarily in the cache.

The memory hierarchy is developed to improve the average memory access time and consequently, the average execution time of programs. However, such design approach, which is typically found in Commercial Off-the-shelf (COTS) platforms, is a source of unpredictability in the context of real-time systems. Cache properties like data replacement strategy, size, organization and access order influence the cache hit/miss ratio and make it difficult to predict cache

<sup>&</sup>lt;sup>2</sup>The main memory is usually found outside the processor chip.

behaviour. Besides these properties, one needs also to consider the interference due to task *pre-emptions* (when one task is interrupted during execution to allow another, usually more urgent, task to execute) and *migrations* (when one task resumes its execution in a different core than the one where it was executing before being interrupted) which incur additional cache misses.

In this dissertation, we assume that the platform follows an hierarchy equal to the one depicted in Figure 2.1. However, caches and main memory are treated as black boxes. In fact, in the literature it is possible to find several works that are devoted to the topic of adding predictability to caches. The interested reader may look for the following work as a starting point [Gracioli et al., 2015].

#### 2.2.3 Memory Bus

Cache unpredictability is not the only problem that is found when using a memory hierarchy similar to the one depicted in Figure 2.1. There is another important problem that arises from the way that memory is designed. If one looks carefully to the memory hierarchy depicted in Figure 2.1, one may easily see that with the exception of private memory levels, multicore processors share paths to the different levels in the memory hierarchy. These paths are part of the system memory bus and because they are shared, they may lead to contention when more than one core simultaneously perform a memory request to the same shared level of memory. For instance, when a memory request is made to main memory or even level L2.

In order to avoid the undesired effects of bus contention, COTS manufacturers add arbitration mechanisms to the system memory bus. Nevertheless, the arbiters employed in general-purpose systems are: (1) often undocumented and their implementation is hidden; (2) not controlled by the operating system and consequently, the exact time instants at which the memory requests are made are unknown as they are a result of cache misses; and (3) unfair and consequently may re-order memory requests (subject to the arbiter's own rules) and neglect task priorities (which are defined at the operating system level) in order to optimize, for instance, memory bandwidth [Dasari et al., 2013]. Thus, these arbitration mechanisms have a direct impact on system performance and the response time of tasks. In fact, if their behaviour is not accounted for in the WCET analysis of the tasks composing a system, the actual worst-case time observed at runtime may drastically deviate from the predictions made at design time.

The memory bus contention problem is a well-known problem in the real-time systems community and several authors have already devoted their efforts to it. In the following paragraphs, we cover the most relevant work that has been done in the research of the memory bus contention problem.

Deterministic architectures (such as MERASA [Ungerer et al., 2010], PRET [Lickly et al., 2008]) consisting of mechanisms to control interference at the hardware level have already been proposed in the past. Nevertheless, this type of solutions is very specific, leading the stakeholders (usually due to the costs involved in the development of specific hardware platforms) to adopt general-purpose platforms to implement their products.

#### 2.2.3.1 Time-Driven vs. Event-Driven Approaches

Arbitration approaches can be classified into two distinct classes [Abel et al., 2013]: time-driven and event-driven.

Time-driven approaches, such as the ones proposed in [Kelter et al., 2011], [Chattopadhyay et al., 2010], [Schranzhofer et al., 2010], employ Time-division Multiple Access (TDMA) as the bus arbitration policy. The idea behind these approaches is to time-partition the access to the bus into time slots and generate a bus schedule. At runtime, the arbiter uses the generated bus schedule to grant permission to a given core to access the bus. A core is allowed to access the bus if the current time slot is assigned to that core, otherwise the core has to wait until the next available time slot that is assigned to it. TDMA-based approaches provide temporal isolation between cores and thus have the advantage of allowing each core to be analysed in an independent manner. As each core may only perform memory requests in its assigned time slot, cores cannot interfere with each other. However, for memory operations to be efficient there must be an alignment between memory requests and each core's assigned slots, otherwise many slots may be wasted.

Event-based approaches provide bounds on the interference that a resource may suffer in a worst-case scenario by knowing the maximum number of memory accesses that a task may request and the arbitration policy of a given resource.<sup>3</sup> Some works in the literature ([Pellizzoni et al., 2010], [Schliecker et al., 2010]) use the concept of arrival curves [Thiele et al., 2000]. For instance, in [Pellizzoni et al., 2010] arrival curves are used to model the maximum amount of memory traffic produced by all tasks executing in a given core in a given time interval. Then, the derived curves are used to compute bounds on the delay incurred by a given task considering the arrival curves derived for the cores not executing the analysed task and peripheral buses. In [Schliecker et al., 2010], arrival curves are used to model the load of each processor in the system. Other works, as for instance [Ivers et al., 2006], estimate the maximum delay a task may suffer due to memory interference when executing in a system where resources are shared.

#### 2.2.3.2 Co-Scheduling Approaches

Co-scheduling approaches have also been proposed to circumvent the memory bus contention problem. The idea behind such approaches is to decouple memory requests from the actual task's execution such that all the code and data needed during execution are loaded in a core's local memory before beginning the task's execution. By pre-loading the task's code and data in the core's local memory, a core can execute the task without suffering any kind of interference.

Co-scheduling was the target of research in [Schranzhofer et al., 2010] where the authors analyse different resource access models. In particular, depending on the studied model, accesses to shared resources either occur in specific phases (as in a pure co-scheduling approach) or occur, without any restriction, throughout the task's execution. The objective of that study was to evaluate which model performs better, considering the interaction with shared resources, in terms of worst-case response times and schedulability. The conclusion is that a model with 3 phases is the one that

<sup>&</sup>lt;sup>3</sup>In this context, a worst-case scenario is a scenario that maximizes the effects of interference on memory requests.

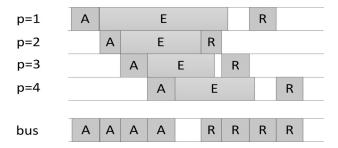

Figure 2.2: Example of a 3-phase task model schedule

performs best when compared to models where no restriction is posed on the accesses to shared resources.

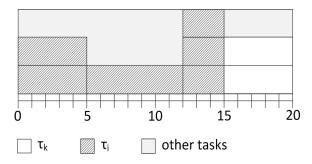

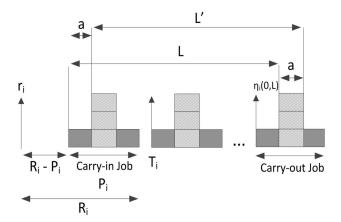

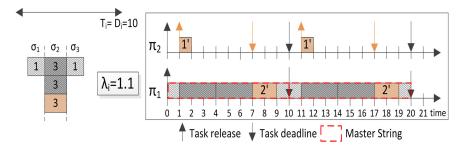

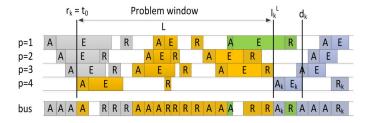

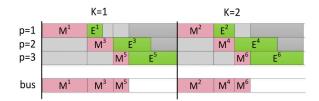

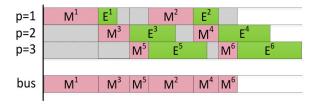

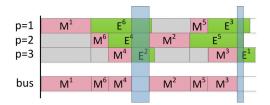

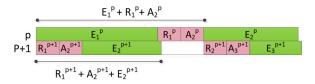

The 3-phase task model is a generalization of the PRedictable Execution Model (PREM) [Pellizzoni et al., 2011]. In PREM, tasks consist of only two phases (known as the predictable intervals): a memory phase and an execution phase. In the memory phase, tasks fetch data and instructions from main memory into the core's local memory while in the execution phase, tasks execute without requiring any access to the shared memory and thereby minimizing any possible interference during their execution. The 3-phase task model generalizes PREM by adding a third phase in which the modified data is pushed back from the core's local memory into the main memory. Moreover, tasks that follow this execution model never access the bus during their execution phase, instead, all the bus accesses are performed during the first and third phases. Figure 2.2 depicts a schedule where four tasks execute in a multiprocessor platform, each executing in a processor. The memory phases (A and R, where A stands for *Acquisition* and R stands for *Restitution*) require the use of the bus while the execution phases (in the figure represented by the letter E) do not require any access to the memory bus.

The 3-phase task model has been subject to experiments carried out to evaluate the applicability of the model in different domains. In [Durrieu et al., 2014a], the authors use the 3-phase task model to model periodic tasks in a flight management system. Moreover, in [Girbal et al., 2015], the authors show that executing tasks in a multicore system leads to increases in the WCET measured in isolation of up to 3x the value in isolation, and that by using the 3-phase task model it is possible to obtain an interference-free execution in a multicore system. A similar observation was made in [Nowotsch and Paulitsch, 2012] where the authors evaluate the effects of having multiple applications of different criticality levels executing in a multicore platform. More precisely, the authors observed a maximum slowdown of 5.1x in application execution when multiple cores access network and memory concurrently. Both of these results show that special care must be taken when executing safety-critical applications in multicore platforms due to the increase in WCET as a result of interference related to concurrent accesses to shared resources. A similar result to both of these works is presented in Chapter 5.

In [Becker et al., 2016], the 3-phase task model is applied to AUTOSAR applications in order to obtain a contention free execution in a many-core architecture. In [Tabish et al., 2016], the authors integrate the 3-phase task model with TDMA managed accesses to a system bus, as a

way to serialize memory phases in multicore operating systems for embedded scratchpad-based multicore architectures.

None of the above mentioned works tackle the problem of how to globally schedule 3-phase tasks in a multicore system. To the best of our knowledge, the only work that provides a solution to this problem is the work presented by Alhammad and Pellizzoni [Alhammad, 2016; Alhammad and Pellizzoni, 2014]. In this dissertation, we fill that gap in the literature and propose in Chapter 5 a solution to this problem that improves the work proposed by [Alhammad, 2016; Alhammad and Pellizzoni, 2014].

#### 2.3 Multiprocessor Scheduling

Before presenting the most important concepts of real-time multiprocessor scheduling, let us present some properties of scheduling algorithms that are useful for understanding some concepts proposed in this dissertation.

A scheduling algorithm is said to be *preemptive* if it is capable of suspending a job during execution and later resume it from the point where it was suspended. Usually, preemption operations occur due to the arrival of higher priority tasks into the system. A *non-preemptive* scheduling algorithm does not suspend tasks. Once the tasks are allocated into the processor, tasks execute continuously until completion, time instant at which another task is selected for execution. A scheduling algorithm is said to be *work-conserving* if it never idles a processor when there is a ready task<sup>4</sup> waiting to be executed. A scheduling algorithm is said to be *optimal* if it schedules all the task sets that are feasible and that abide by the task model.

Two important metrics are used to quantitatively compare different scheduling algorithms: the utilization bound and resource augmentation bound ([Kalyanasundaram and Pruhs, 1995] and [Phillips et al., 1997]).

The *utilization bound* of a given scheduling algorithm A on a platform  $\Pi$ , consisting of m unit-speed processors, is defined as the largest utilization  $U_b$  such that all implicit-deadline task sets composed of sequential tasks with utilization  $U \leq U_b$  are deemed schedulable by A when executed in platform  $\Pi$ .

While the utilization bound is based on the utilization factor and therefore on the properties of the task set, a resource augmentation bound quantifies the processor speed-up factor with respect to an optimal scheduling algorithm. That is, it quantifies how much one has to increase the processor speed in order to guarantee the schedulability of a task set using a given scheduling algorithm *A* instead of an optimal one.

Formally, a scheduling algorithm A has a resource augmentation bound b on a given platform  $\Pi$ , consisting of m unit-speed processors, if it successfully schedules all the feasible task sets, which are schedulable by an optimal algorithm on  $\Pi$ , on a platform where the processors are b times as fast than the ones in  $\Pi$ .

Real-time multiprocessor scheduling theory deals with two problems [Davis and Burns, 2011a]:

<sup>&</sup>lt;sup>4</sup>A ready task is a task that is waiting for access to the processor.

- the *allocation problem* the decision problem of how a set of *n* tasks should be allocated on a set of *m* processors;

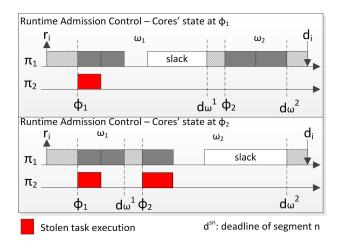

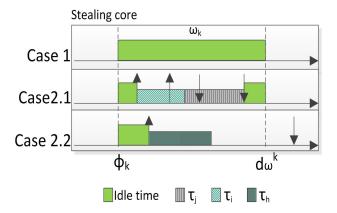

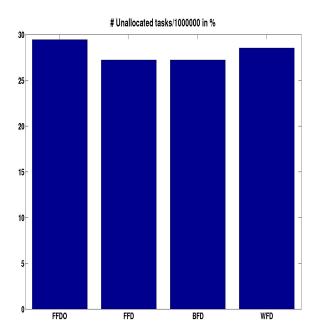

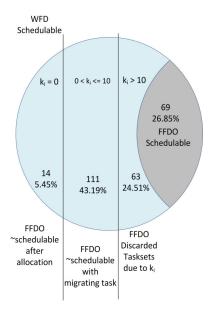

- the *priority problem* the decision problem of choosing the order a set of tasks should follow so that each task's deadline is met.