# REVERT: Runtime Verification for Real-Time Systems

Sangeeth Kochanthara, Geoffrey Nelissen, David Pereira, Rahul Purandare sangeeth1455@iiitd.ac.in, {grrpn,dmrpe}@isep.ipp.pt, purandare@iiitd.ac.in

# Runtime Verification of Real-Time Systems

#### Limitations of classic (static) approaches:

- Number of reachable states too large for testing

- Potential blow-up when automatically exploring the system's statespace (e.g., model-checking)

- Limited automation in machine assisted proof construction tools (e.g., SMT solvers, proof-assistants)

- Difficulties in capturing data expected to be available only at runtime (need for abstraction leads to lack of precision)

#### <u>Limitations of existing Runtime Verification</u> solutions:

- Vast majority of tools developed for non-real-time applications;

- In most cases, it is difficult to capture extra-functional properties:

- either no support at all; or

- via complex specifications that are not accessible for the non-expert or the typical industrial practitioner

- Lack of a specification language that is user friendly, and that allows to capture distinct classes of timing properties

### The REVERT Framework

#### 1) A new specification language:

- Intuitive, easy to use domain specification language

- Capture changes in the system via guarded state-machine transitions between nodes (monitor states)

- Functional behavior as extended regular expressions

- Support for associating events with job specifications

- Three classes of timing constraints relevant for real-time systems: time, duration and jitter.

- Timing constraint on sequences of events,

- Execution time of a job,

- Jitter on time and duration.

- Local variables and local code (e.g., for monitor) initialization, calling counter-measure actions, etc)

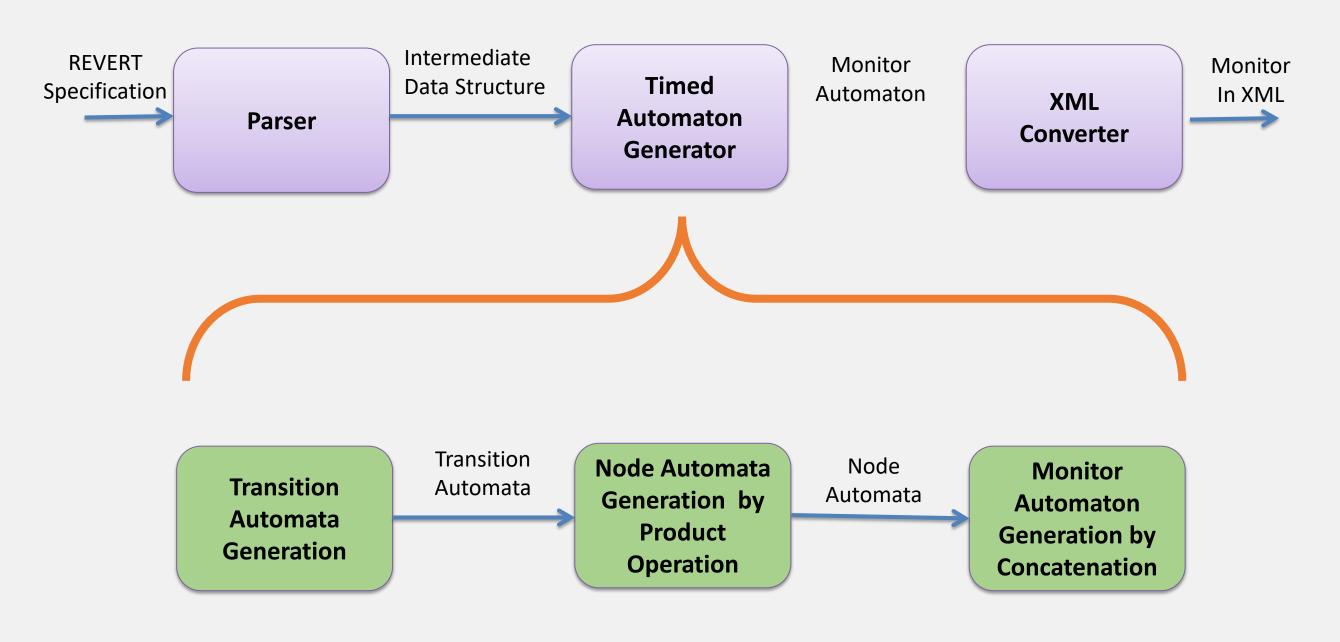

#### 2) A new monitor generation process:

- 1. REVERT specifications are parsed into intermediate datastructure;

- 2. Generation of the corresponding automata (via combination of intermediate types of finite automata)

- 3. Translation of the generated timed state-machine into XML format

# Transition generation algorithm for timing constraints

```

1 every state state_i is associated with two variables REex_i and REel_i;

2 add start state (state_0) to the set waiting\_states;

3 reset clock variable main\_clock;

4 REex_0 := \alpha;

5 REel_0 := 0;

6 for all state_i \in waiting states do

for all \xi \in \Sigma do

if \mathcal{D}_{\varepsilon}(REex_i) \neq 0 then

if \exists state_j \in waiting\_states \ s. \ t. \ \mathcal{D}_{\xi}(REex_i) \in REex_i \ \mathbf{then}

REel_i := REel_i \vee \mathcal{I}_{\xi}(REel_i);

else if \mathcal{D}_{\xi}(REex_i) = 1 then

create a new final state state_j;

REex_j := 1;

REel_i := \mathcal{I}_{\mathcal{E}}(REel_i);

add a new state state_i to waiting\_states;

REex_j := \mathcal{D}_{\xi}(REex_i);

17

REel_i := \mathcal{I}_{\varepsilon}(REel_i);

\mathbf{end}

create a transition from state_i to state_j;

\mathbf{else}

LSI := longest suffix of \mathcal{I}_{\xi}(REel_i) matched with REel_j for any state

state_j \in waiting \ states;

if LSI is empty then

create a transition from state_i to state_0;

else if length of LSI = 1 then

create a self-loop on state_i with main\_clock reset;

\mathbf{else}

add an auxiliary clock aux\_clk_i;

RE_{pre} := \text{longest prefix of } \mathcal{I}_{\xi}(REel_i) \text{ before } LSI;

reset aux\_clk_i at state_k \in waiting\_states s. t. RE_{pre} = REel_k;

create a transition from state_i to state_j with main\_clock set to value of

aux\_clk_i;

32

end

end

end

35 end

```

Transition automaton generation algorithm for time operator

## **Example Specification**

```

use "T_Events.ev"

c2: \operatorname{duration}(\operatorname{Job1}) \leq 10;

use "Ext_Procs.h";

transitions {

monitor MyMon {

fail_blocked_time: failure(c1) \rightarrow

RecoveryMode

observe { arrT, startT, suspT, blockedT,

failureReason := 1;

resumeT, unblockedT, complT }

recover_from_blocking();

variables { failureReason : integer; }

fail\_duration: failure(c2) \rightarrow RecoveryMode

failureReason := 2;

recover_from_duration();

jobs {

Job1 {

start: {startT}

suspend: {suspT, blockedT}

resume: {resumeT, unblockedT}

node RecoveryMode {

complete: {complT}

init{}

initializeSystemRecovery();

constraints {

nodes { NormalMode, RecoveryMode }

c1[ERE]: _ complT;

initial { NormalMode }

transitions {

job\_completion: success(c1) \rightarrow

node NormalMode {

init{}

NormalMode;

resetAllSystemFlags();

constraints {

c1: time(blockedT resumeT)) \leq 2;

```

## Concluding Remarks

- New specification language for runtime verification of RTSs

- Novel method to generate timed finite state machines that avoids state blowup in run-time

- Implemented the framework as a tool-chain

CISTER Research Unit (CEC/04234), co-financed by:

facebook.com/cisterrealtime

4249-015 Porto, Portugal