## **BEng Thesis**

# **Exploring IVSHMEM in the Jailhouse Hypervisor**

Orientação científica: Cláudio Maia

#### **Diana Ramos**

CISTER-TR-191211

#### Exploring IVSHMEM in the Jailhouse Hypervisor

#### Diana Ramos

**CISTER Research Centre**

Polytechnic Institute of Porto (ISEP P.Porto)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8321159

E-mail:

https://www.cister-labs.pt

#### Abstract

Nowadays, modern multicore processors come with virtualization featuresthat provide the creation of different virtual environments inside the samemachine, which magnify its ability to use all the resources available. The combination of multiprocessor systems with virtualization is highly demanded by the embedded systems domain. Virtualization technologies like hypervisor software are responsible for managing virtual machines and control their access to physical resources. Severalvirtualization technologies and hypervisors exist for different industrydomains. One of those, is Jailhouse, a static partitioning hypervisor that partitions the hardware resources and directly assigns applications to each partition, providing them with access to the actual physical resources. This hypervisor focuses on giving the applications the isolation they need; however this can be seen as a limitation as it may restrict communicationbetween applications running in different partitions. There are inter virtualmachine 19s communication mechanisms (based on networking or sharedmemory)that solves this limitation. This project aims at exploring this aspectin Jailhouse and focuses on using the Jailhouse hypervisor and ashared-memory mechanism to manage to send information between twopartitions. Specifically, it aims at: (1) understanding the jailhouse hypervisor with respectto its features. For that, demonstrations are executed on top of twoarchitectures, Intel based x86-64, using QEMU; and ARM, using a BananaPi-M1 board; and (2) understanding a shared memorybased communication protocol, denoted as IVSHMEM, and create a use case in which two partitions exchange information using this protocol. Results of this work are promising as the x86-64 use case was successfullyexecuted on top of QEMU, however, the ARM use case is still an on-goingendeavour.

# Exploring IVSHMEM in the Jailhouse Hypervisor

CISTER - Centro de Investigação em Sistemas Computacionais Embebidos e de Tempo-Real

2018/2019

# **Exploring IVSHMEM in the Jailhouse**Hypervisor

CISTER - Centro de Investigação em Sistemas Computacionais Embebidos e de Tempo-Real

2018 / 2019

1161209 Diana Ramos

#### **Degree in Computing Engineering**

September of 2019

Advisor: Cláudio Ribeiro Maia

«to my family, that have always supported me»

IV Diana Ramos

### **Acknowledgments**

I would like to thank my adviser Cláudio Maia, David Pereira and Pedro Santos for all the support, availability and interest in helping me in everything I needed during my project.

Moreover I would like to thank CISTER members that provided me with good moments and support and CISTER overall for the internship opportunity.

VI Diana Ramos

#### **Abstract**

Nowadays, modern multicore processors come with virtualization features that provide the creation of different virtual environments inside the same machine, which magnify its ability to use all the resources available. The combination of multiprocessor systems with virtualization is highly demanded by the embedded systems domain.

Virtualization technologies like hypervisor software are responsible for managing virtual machines and control their access to physical resources. Several virtualization technologies and hypervisors exist for different industry domains. One of those, is Jailhouse, a static partitioning hypervisor that partitions the hardware resources and directly assigns applications to each partition, providing them with access to the actual physical resources.

This hypervisor focuses on giving the applications the isolation they need; however this can be seen as a limitation as it may restrict communication between applications running in different partitions. There are inter virtual machine's communication mechanisms (based on networking or shared-memory) that solves this limitation. This project aims at exploring this aspect in Jailhouse and focuses on using the Jailhouse hypervisor and a shared-memory mechanism to manage to send information between two partitions.

Specifically, it aims at: (1) understanding the jailhouse hypervisor with respect to its features. For that, demonstrations are executed on top of two architectures, Intel based x86-64, using QEMU; and ARM, using a Banana Pi-M1 board; and (2) understanding a shared memory-based communication protocol, denoted as IVSHMEM, and create a use case in which two partitions exchange information using this protocol.

Results of this work are promising as the x86-64 use case was successfully

executed on top of QEMU, however, the ARM use case is still an on-going endeavour.

**Keywords (Theme):** embedded systems, virtualization, isolation. **Keywords (Technologies):** hypervisor, Jailhouse, QEMU, Banana Pi-M1,

TCP/IP, shared memory, IVSHMEM.

VIII Diana Ramos

#### Resumo

Hoje em dia, os processadores modernos com vários cores já vêm com virtualização que fornece a criação de diferents ambientes virtuais dentro da mesma máquina, o que permite usar de melhor forma os recursos disponíveis. Esta combinação de sistemas multiprocessador com virtualização é altamente procurada no domínio de sistemas embebidos.

Tecnologias de virtualização como o hipervisor é responsável por gerir máquinas virtuais e controlar o acesso aos recursos físicos. Estas tecnologias e hipervisores existem para diferentes domínios da indústria. Um desses é Jailhouse, um hipervisor de particionamento estático que particiona o hardware e atribui diretamente a aplicações de cada partição, fornecendo acesso aos recursos físicos.

Este hipervisor foca se em isolar as aplicações. No entanto, o isolamento pode ser visto como uma inconveniência pois podes limitar a comunicação entre aplicações de partições diferentes. Existem mecanismos de comunicação entre máquinas virtuais (via rede ou memória partilhada) que vem a resolver esta limitação. Este projeto foca-se em explorar o Jailhouse e um mecanismo de memória partilhada de forma a que duas partições sejam capazes de receber informação uma da outra.

Especificamente, o projeto tem os seguintes objetivos: (1) perceber as funcionalidades do Jailhouse, correndo demonstrações em várias arquiteturas: Intel x86-64 utilizando o QEMU e em ARM usando a placa Banana Pi-M1 e (2) entender o funcionamento de um mecanismo de memória partilhada chamado de IVHSMEM e criar um caso de uso onde duas partições comunicam uma com a outra utilizando esse protocolo.

Os resultados deste trabalho provaram ser promissores visto que tanto o hipervisor como as demonstrações correram nas várias arquiteturas (x86-

64 e ARM) com sucesso, no entanto o caso de uso em ARM utilizando IVSHMEM é um trabalho ainda em andamento.

Palavras-chave (Tema): sistemas embebidos, virtualização, isolamento.

Palavras-chave (Tecnologias): hypervisor, Jailhouse, QEMU, Banana Pi-M1, TCP/IP, memória partilhada, IVSHMEM.

## **Contents**

| Al | bstra | ct      |                              | ١   | /II |

|----|-------|---------|------------------------------|-----|-----|

| R  | esum  | 0       |                              |     | IX  |

| Li | st of | Figure  | s                            | X   | ۲V  |

| A  | crony | ms      |                              | X۱  | /II |

| 1  | Intro | oductio | on                           |     | 1   |

|    | 1.1   | Projec  | ct Context                   | ·   | 2   |

|    |       | 1.1.1   | Problem Description          |     | 3   |

|    |       | 1.1.2   | Approach                     |     | 4   |

|    |       | 1.1.3   | Objectives and Contributions |     | 5   |

|    |       | 1.1.4   | Organization                 |     | 5   |

|    | 1.2   | Repor   | rt Structure                 |     | 6   |

|    | 1.3   | Work    | Planning                     |     | 6   |

|    |       | 1.3.1   | Meetings                     |     | 6   |

| 2  | Stat  | e-of-A  | rt                           |     | 9   |

|    | 2.1   | Hyper   | visors                       |     | 9   |

|    |       | 2.1.1   | Hypervisor's Classification  |     | 9   |

|    |       | 2.1.2   | The KVM Hypervisor           | . 1 | 10  |

|    |       | 2.1.3   | The Xen Hypervisor           |     | 11  |

|    |       | 2.1.4   | The Jailhouse Hypervisor     | . 1 | 12  |

|    | 2.2   | Inter-\ | VM Communication             | . 1 | 13  |

|   |                     | 2.2.1                                                                                    | TCP/IP-based Communication                                                                                                                                                                                                        | 13                                                 |

|---|---------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   |                     | 2.2.2                                                                                    | Shared-Memory Communication                                                                                                                                                                                                       | 14                                                 |

| 3 | Jail                | house                                                                                    | Hypervisor                                                                                                                                                                                                                        | 17                                                 |

|   | 3.1                 | Jailho                                                                                   | use Overview                                                                                                                                                                                                                      | 17                                                 |

|   |                     | 3.1.1                                                                                    | Code Organization                                                                                                                                                                                                                 | 19                                                 |

|   |                     | 3.1.2                                                                                    | Jailhouse Requirements                                                                                                                                                                                                            | 20                                                 |

|   |                     | 3.1.3                                                                                    | Linux Kernel Modules                                                                                                                                                                                                              | 23                                                 |

|   |                     | 3.1.4                                                                                    | Jailhouse's Kernel Module                                                                                                                                                                                                         | 25                                                 |

|   |                     | 3.1.5                                                                                    | Jailhouse Functionality                                                                                                                                                                                                           | 27                                                 |

|   |                     | 3.1.6                                                                                    | Jailhouse's Cell States                                                                                                                                                                                                           | 30                                                 |

|   |                     | 3.1.7                                                                                    | Run Time Failing Errors                                                                                                                                                                                                           | 30                                                 |

|   | 3.2                 | Jailho                                                                                   | use's Demonstrations                                                                                                                                                                                                              | 32                                                 |

|   |                     | 3.2.1                                                                                    | QEMU Demonstration                                                                                                                                                                                                                | 33                                                 |

|   |                     | 3.2.2                                                                                    | Banana Pi Board                                                                                                                                                                                                                   | 39                                                 |

|   |                     |                                                                                          |                                                                                                                                                                                                                                   |                                                    |

| 4 | IVS                 | НМЕМ                                                                                     | - The Inter-Vm SHared Memory                                                                                                                                                                                                      | 43                                                 |

| 4 | <b>IVS</b> I<br>4.1 |                                                                                          | •                                                                                                                                                                                                                                 | <b>43</b>                                          |

| 4 |                     |                                                                                          | n of IVSHMEM                                                                                                                                                                                                                      |                                                    |

| 4 |                     | Desig                                                                                    | n of IVSHMEM                                                                                                                                                                                                                      | 43<br>44                                           |

| 4 |                     | Design                                                                                   | The Configuration Section                                                                                                                                                                                                         | 43<br>44                                           |

| 4 |                     | Design<br>4.1.1<br>4.1.2<br>4.1.3                                                        | The Configuration Section                                                                                                                                                                                                         | 43<br>44<br>45                                     |

| 4 | 4.1                 | Design<br>4.1.1<br>4.1.2<br>4.1.3                                                        | The Configuration Section                                                                                                                                                                                                         | 43<br>44<br>45<br>45<br>46                         |

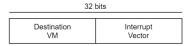

| 4 | 4.1                 | Design<br>4.1.1<br>4.1.2<br>4.1.3<br>Messa<br>4.2.1                                      | The Configuration Section  The Base Address Registers  The Register Memory  age Signaled Interrupts                                                                                                                               | 43<br>44<br>45<br>45<br>46                         |

| 4 | 4.1                 | Design<br>4.1.1<br>4.1.2<br>4.1.3<br>Messa<br>4.2.1                                      | The Configuration Section                                                                                                                                                                                                         | 43<br>44<br>45<br>45<br>46<br>47                   |

| 4 | 4.1                 | Design<br>4.1.1<br>4.1.2<br>4.1.3<br>Messa<br>4.2.1<br>Jailho                            | The Configuration Section The Base Address Registers The Register Memory age Signaled Interrupts MSI's Functionality use's Version of IVSHMEM IVSHMEM Demonstration                                                               | 43<br>44<br>45<br>45<br>46<br>47                   |

| 4 | 4.1                 | Design<br>4.1.1<br>4.1.2<br>4.1.3<br>Messa<br>4.2.1<br>Jailho<br>4.3.1<br>4.3.2          | The Configuration Section The Base Address Registers The Register Memory age Signaled Interrupts MSI's Functionality use's Version of IVSHMEM IVSHMEM Demonstration IVSHMEM Demonstration on Banana Pi-M1                         | 43<br>44<br>45<br>45<br>46<br>47<br>47             |

| 4 | 4.1<br>4.2<br>4.3   | Design<br>4.1.1<br>4.1.2<br>4.1.3<br>Messa<br>4.2.1<br>Jailho<br>4.3.1<br>4.3.2          | The Configuration Section The Base Address Registers The Register Memory age Signaled Interrupts MSI's Functionality use's Version of IVSHMEM IVSHMEM Demonstration IVSHMEM Demonstration on Banana Pi-M1 Solution Implementation | 43<br>44<br>45<br>45<br>46<br>47<br>47<br>48<br>51 |

|   | 4.1<br>4.2<br>4.3   | Design<br>4.1.1<br>4.1.2<br>4.1.3<br>Messa<br>4.2.1<br>Jailho<br>4.3.1<br>4.3.2<br>4.3.3 | The Configuration Section The Base Address Registers The Register Memory age Signaled Interrupts MSI's Functionality use's Version of IVSHMEM IVSHMEM Demonstration IVSHMEM Demonstration on Banana Pi-M1 Solution Implementation | 43<br>44<br>45<br>46<br>47<br>47<br>48<br>51<br>52 |

|    | 5.3   | Final Appreciation                       | 50 |

|----|-------|------------------------------------------|----|

| Bi | bliog | raphy                                    | 60 |

| At | tachr | ments                                    |    |

| Α  | Sett  | ing up Jailhouse with BPI-M1             | 66 |

|    | A.1   | Formatting BPI-M1 sd Card                | 66 |

|    | A.2   | Adjust U-boot                            | 67 |

|    | A.3   | Cross Compiling Kernel for ARM on x86    | 67 |

|    | A.4   | Installing the Linux kernel on BPI-M1    | 68 |

|    | A.5   | Cross Compiling Jailhouse for ARM on x86 | 69 |

|    | A.6   | Installing jailhouse                     | 69 |

|    | A.7   | GIC-demo's Outputs                       | 71 |

| В  | Jaill | nouse's IVSHMEM related files            | 72 |

|    | B.1   | IVSHMEM Demonstration Configuration File | 72 |

|    | B.2   | IVSHMEM Demonstration Inmate File        | 76 |

|    | B.3   | IVSHMEM 2.0                              | 82 |

|    | B 4   | Parking Errors                           | 84 |

## **List of Figures**

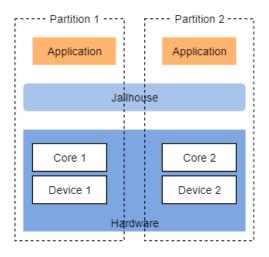

| 1.1  | Static partitioning example                                    | 3  |

|------|----------------------------------------------------------------|----|

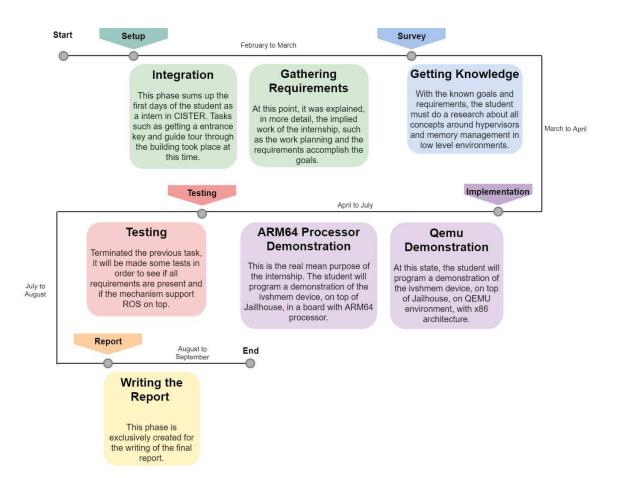

| 1.2  | Tasks and milestones by chronologic order                      | 7  |

| 1.3  | Meetings table                                                 | 8  |

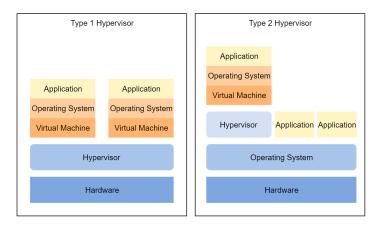

| 2.1  | Hypervisor's type 1 and 2 designs                              | 10 |

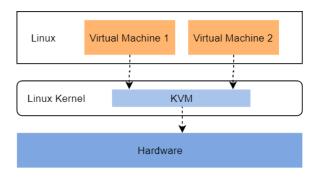

| 2.2  | Basic architecture of the KVM Hypervisor                       | 11 |

| 2.3  | Basic architecture of the Xen Hypervisor                       | 12 |

| 2.4  | Basic architecture of a system using the Jailhouse Hypervisor. | 13 |

| 2.5  | Basic architecture of TCP/IP protocol                          | 14 |

| 2.6  | Basic architecture of shared memory communication protocol.    | 15 |

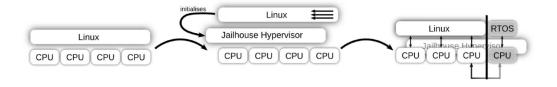

| 3.1  | Jailhouse bootstrap process taken from [40]                    | 17 |

| 3.2  | Jailhouse's system architecture taken from [14]                | 18 |

| 3.3  | Jailhouse's package diagram                                    | 19 |

| 3.4  | Jailhouse's hardware requirements for both architectures       | 22 |

| 3.5  | Jailhouse's software requirements for both architectures       | 23 |

| 3.6  | Loaded modules                                                 | 25 |

| 3.7  | Kernel module transactions adapted from [15]                   | 26 |

| 3.8  | Jailhouse installation Makefile                                | 26 |

| 3.9  | Jailhouse's command line tool options                          | 27 |

| 3.10 | Jailhouse's hypercall cell states                              | 30 |

| 3.11 | Jailhouse cell states                                          | 31 |

| 3.12 | Jailhouse unhandled traps message                              | 32 |

| 3.13 | Jailhouse unhandled trap console message                       | 32 |

| 3.14 | Jailhouse unhandled traps conditions               | 32 |

|------|----------------------------------------------------|----|

| 3.15 | Jailhouse parking error                            | 33 |

| 3.16 | QEMU architecture                                  | 33 |

| 3.17 | QEMU images list                                   | 36 |

| 3.18 | Bash history for QEMU's AMD systems                | 36 |

| 3.19 | PIC architecture taken from [22]                   | 37 |

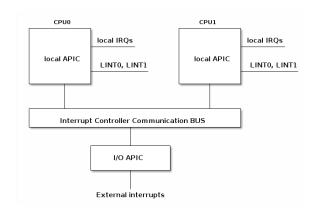

| 3.20 | APIC architecture taken from [22]                  | 38 |

| 3.21 | BananaPi-M1 specification                          | 39 |

| 4.1  | IVSHMEM or Nahanni's overview adapted from [32]    | 44 |

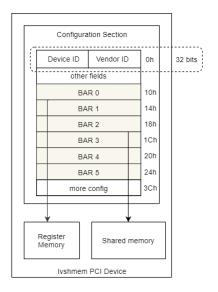

| 4.2  | IVSHMEM PCI device architecture adapted from [32]  | 45 |

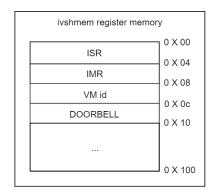

| 4.3  | IVSHMEM PCI device registers adapted from 4.3      | 46 |

| 4.4  | IVSHMEM PCI device doorbell adapted from 4.3       | 46 |

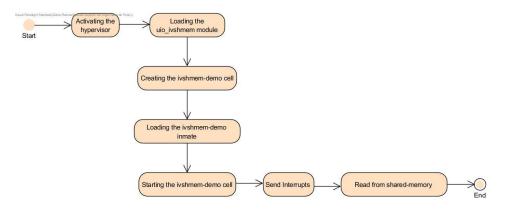

| 4.5  | Activity diagram of IVSHMEM demonstration          | 51 |

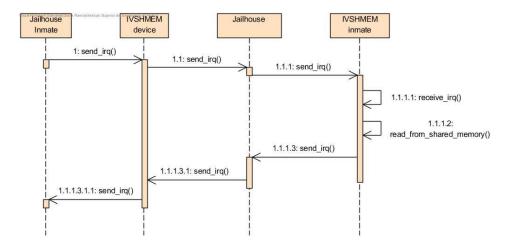

| 4.6  | Sequence diagram for IVSHMEM demonstration         | 52 |

| 47   | Finding the device function in ivshmem-demo inmate | 53 |

### **Acronyms**

**AMD** Advanced Micro Devices

**AMD-V** Advanced Micro Devices Virtualization

AMD64 Advanced Micro Devices 64

**ARM** Acorn Risc Machine

**APIC** Advanced Programmable Interrupt Controller

**BPI** Banana Pi-M1

**CPU** Central Processor Unit

CISTER Centro de Investigação em Sistemas Computacionais Embebidos

e de Tempo-Real

**DTB** Device Tree Binarie

**DMA** Direct Memory Access

**DHCP** Dynamic Host Configuration Protocol

**EPT** Extended Page Tables

**FUSE** Filesystem in Userspace

**GIC** Generic Interrupt Controller

**HVM** Hardware Virtual Machine

I/O Input/Output

IOMMU I/O Memory Management Unit

ISEP Instituto Superior de Engenharia do Porto

**IPC** Inter Process Communication

**IVSHMEM** Inter-VM SHared MEMory

**IP** Internet Protocol

**IRQ** Interrupt Requests

ISR Interrupt Status Register

**IMR** Tnterrupt Mask Register

KVM Kernel Virtual Machine

**LAPIC** Local APIC

MMIO Memory-Mapped for the I/O

**MSI** Message Signaled Interrupts

MSI-X Message Signaled Interrupts-X

**NPT** Nested Page Tables

**OS** Operating System

**PCI** Peripheral Component Interconnect

**POSIX** Portable Operating System Interface

**PSCI** Power State Coordination Interface

**PPI** Private Peripheral Interrupt

PESTI Projeto Estágio

**QEMU** Quick Emulator

**RTOS** Real Time Operating System

**SPARC** Scalable Processor ARChitecture

**SVM** Secure Virtual Machine

**SPI** Shared Peripheral Interrupt

**SDL** Simple DirectMedia Layer

**SGI** Software Generated Interrupt

**TCP** Transmission Control Protocol

**UDP** User Datagram Protocol

**UIO** Userspace I/O

VM Virtual Machine

**VT** Virtualization Technology

VT-d Virtualization Technology for Directed I/O

**VCPU** Virtual CPU

VMX Virtual Machine Extension

**VNC** Virtual Network Computing

#### 1. Introduction

Virtualization is a technique that allows one to logically divide the system resources between the applications executing on top of it [51]. There are multiple ways of achieving virtualization. For instance, using desktop virtualization <sup>1</sup>, server virtualization <sup>2</sup> or even hardware virtualization, the topic of study of the work reported in this document.

By definition, hardware virtualization occurs at the hardware level, that is, hardware virtualization targets hardware machine resources (such as main memory, hard disks, processor, network related hardware and peripheral devices) to create an abstraction layer for each of these resources. In a hardware virtualization setting, there is an intermediate layer between the hardware tier and software tier named the hypervisor layer [42] [32].

A hypervisor is a virtualization software that enables the creation and management of Virtual Machines (VMs) [16] often called "guests" executing over a physical machine, denoted as "host". There are many hypervisors out there in the market, each with its own purpose, as for instance Xen [55] and Kernel Virtual Machine (KVM) [54], Jailhouse [40] and many more, however in this report the attention is devoted to the Jailhouse hypervisor.

The Jailhouse hypervisor is a static partition-based hypervisor that separates the machine's available hardware resources into persistent divisions, denoted as partitions or "cells" in Jailhouse terminology, to which one may assign different types of applications, denoted as "inmates" in Jailhouse terminology. These applications include bare-metal applications or operat-

<sup>&</sup>lt;sup>1</sup>Desktop virtualization is the virtualization of workstations, allowing multiple users to remotely access each one of them logically [34].

<sup>&</sup>lt;sup>2</sup>Server virtualization enables the creation of multiple virtual environments with one physical server [34].

ing systems (OS), including Linux and other specific operating systems for embedded devices such as Real-time Operating Systems (RTOS)<sup>3</sup>. One of the features provided by Jailhouse is the isolation between partitions [24]. Figure 1.1 depicts an example of how Jailhouse partitions the hardware by the cells. In the example, there are two cells where each one has access to one core and a device (representing for instance a network card, a hard drive, a bus, etc.). In the context of the cell, one can assign inmates (i.e., applications or OSes), with the guarantee that they execute in isolation in their own environment.

Isolation has its advantages (as for instance it allows cells to execute in their own context and therefore avoid being interfered or share their resources with other cells) but at the same time it brings the challenge of how two applications in different cells can share information among them.

The project described in this report focuses on the Jailhouse hypervisor and the challenge of exchanging information between different partitions in order to transfer data between them. Due to the isolation provided by Jailhouse one has to use specific protocols to exchange information such as networking mechanisms like TCP/IP protocol or shared-memory based mechanisms like Inter-VM SHared MEMory (IVSHMEM or Nahanni)<sup>4</sup>.

In this report the focus is on the shared-memory mechanism IVSHMEM.

#### 1.1 Project Context

"Exploring IVSHMEM in the Jailhouse Hypervisor" is a project proposed by CISTER, a research laboratory dedicated to the research of real-time and embedded systems, and is integrated in the curricular unit of PESTI (Projeto Estágio), lectured in Instituto Superior de Engenharia do Porto (ISEP). The subject itself of hypervisors is new to me, so it is a complete challenge

<sup>&</sup>lt;sup>3</sup>RTOS is a type of operating system meant to run applications that need to respond to external events in a timely fashion [53] [9].

<sup>&</sup>lt;sup>4</sup>In this report it will be used IVSHMEM as a reference to this mechanism.

Figure 1.1: Static partitioning example.

to learn something new and popular as it is now and enter in the community with my implementation of it is very satisfying. My main goal by choosing this internship was to diversify my knowledge at a more low-level, so that I would be more receptive to more types of projects.

Alongside with the demands of this job, there are other aspects that I considered, like the type of environment that a research center would have, so that I would be thoughtful about having that experience again in the future.

#### 1.1.1 Problem Description

As mentioned in section 1, Jailhouse is a static partitioning hypervisor that splits the machine's physical resources in divisions (or "cells") in order to assign them to different applications (or "inmates"). As also mentioned, this hypervisor guarantees isolation between the partitions which enables each application to run independently and without any interference from other cells. Yet there are cases where there is the need of exchanging information between different OSes. Thus, in these cases it is imperative to support some kind of communication channel so that partitions can send/receive information without breaking isolation.

Two types of communication mechanisms [23] can be used for this purpose:

networking communication via Transmission Control Protocol/Internet Protocol (TCP/IP), that uses the TCP/IP protocol to send data between nodes or by using shared memory between partitions (example of a protocol that leverages this feature is IVSHMEM).

TCP/IP is a protocol more suitable for those cases where the virtual machines (VMs) reside in separate physical machines, in other words, it was meant to provide a communication channel for multiple physical machines when they need to connect among themselves [41]. However, using communication via TCP/IP is more time consuming considering the data to be transferred goes through the protocol stack <sup>5</sup> [41].

Shared memory is more suitable to those cases where VMs reside in the same physical machine. Thus, it is more suitable to be used in the context of Jailhouse since Jailhouse creates VMs on the same physical machine. Using a shared memory protocol allows one to reduce the number of operations needed to exchange data and the changes are directly visible [41]. Having the above in mind, this project has as main goal the establishment of a shared-memory communication channel using IVSHMEM to enable partitions to exchange information without breaking the partition's isolation.

#### 1.1.2 Approach

Currently, there is already an implementation of IVSHMEM for the Jailhouse hypervisor in x86-64 architecture, provided by Henning Schild and Jan Kiszka.<sup>6</sup>.

Since the available demonstrations regarding x86\_64 architecture of the functionality of Jailhouse are implemented with the support of Quick Emu-

4

<sup>&</sup>lt;sup>5</sup>TCP/IP represents a group of protocol layers. Each layer supports different protocols for managing the data across the network [21].

<sup>&</sup>lt;sup>6</sup>There are two repositories for Jailhouse https://github.com/siemens/Jailhouse, containing the source code, and https://github.com/siemens/Jailhouse-images, containing readyto-use virtual machine with Jailhouse and demonstrations for several architecture types.

lator (QEMU) <sup>7</sup>, the starting point is to learn and understand Jailhouse by following the indications provided by the Jailhouse repository [24] to set up the hypervisor. Then, the hypervisor is executed on an Intel based x86-64 architecture machine, by using QEMU, and a BananaPi-M1 (BPI) board with an ARM processor [6].

After performing the above tasks, a detailed study of the IVSHMEM shared-memory mechanism and the architecture itself (ARM) is done in order to use this mechanism along side with Jailhouse and create a use case where two partitions exchange information between them. This is expected to perform as the already existing implementation for x86\_64 architecture.

#### 1.1.3 Objectives and Contributions

This project aims to: (1) run the Jailhouse hypervisor in x86-64 architecture provided by QEMU emulator, including running already-to-use demonstrations and develop knowledge in this matter and install it in Banana Pi-M1 and run previous demonstrations as well; (2) use the shared-memory mechanism IVSHMEM to function along side with Jailhouse on Banana Pi-M1 to exchange information between two partitions.

#### 1.1.4 Organization

CISTER is an internal research unit of ISEP that specializes in the fields of real-time cyber-physical systems and multiprocessor systems, being rewarded with the highest classification by the Science and Technology Foundation.

Currently, CISTER has international reputation built upon an extensive history of paper publications, international conferences, seminal research works and there's about 60 researchers directly involved with the centre, half of them with a PhD, reaching more than 20 nationalities [3].

<sup>&</sup>lt;sup>7</sup>Open-source Emulator or virtualizer which enables the creation of virtual machines [33]

#### 1.2 Report Structure

This report is structured in the following manner:

The current chapter, **chapter 1**, is an introductory segment that characterizes the problem and the proposed approach and describes the internship itself, including the work division and meetings.

In **chapter 2**, it will be presented the state-of-art of some hypervisors that were considered as possible solutions for the problem at hand (KVM, Xen and Jailhouse) and inter-VM communication mechanisms (TCP/IP protocol and IVSHMEM).

In **chapter 3**, it will be discussed the requirements, functionality, the device driver and one of the demonstrations available for Jailhouse. Ultimately in **chapter 4**, the IVSHMEM will be explained and ran in a x86-64 architecture via QEMU and will be discussed its implementation on a ARM processor board.

Chapter 5 is the conclusions chapter.

#### 1.3 Work Planning

The work can be divided in five different milestones: setup (internship integration and study of the requirements), survey (study of the technologies), implementation (running previous related works and implement some modifications and the specific use case), testing (performance measurements and efficiency tests) and report, as suggested by figure 1.2.

#### 1.3.1 Meetings

There were weekly non-formal meetings and monthly meetings in which the students discussed their work during that week or month. After the discussion of the tasks, it would be defined new tasks for the future.

The table 1.3 summarizes the topics of the meetings.

Figure 1.2: Tasks and milestones by chronologic order.

| Day and Time                             | Members                                                                                                                 | Topics                                                                                                  | Location |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------|

| 15 of March of 2019 at 10 to 11.30 a.m   | <ul><li>Diana Ramos;</li><li>Pedro Chaves;</li><li>Johann Knorr;</li><li>David Pereira;</li><li>Cláudio Maia.</li></ul> | <ul> <li>PESTI's tasks of each student;</li> <li>PESTI's next steps;</li> <li>Other matters.</li> </ul> | CISTER   |

| 1 of April of 2019 at 13:30 to 14:40 a.m | <ul><li>Diana Ramos;</li><li>Pedro Chaves;</li><li>Johann Knorr;</li><li>David Pereira;</li><li>Cláudio Maia.</li></ul> | PESTI's tasks of each student; PESTI's next steps; Other matters.                                       | CISTER   |

| 15 of April of 2019 at 10 to 11.30 a.m   | Diana Ramos;     Pedro Chaves;     Johann Knorr;     David Pereira;     Cláudio Maia.                                   | PESTI's tasks of each student; PESTI's next steps; Other matters.                                       | CISTER   |

Figure 1.3: Meetings table.

#### 2. State-of-Art

In this chapter it is presented some of the current most popular hypervisors, namely KVM, Xen and Jailhouse, requirements and basic functionalities (section 2.1). In addiction, it will be presented some Inter-VMs Communication mechanisms that use networking like TCP/IP protocol and a shared memory protocol named IVSHMEM (section 2.2).

#### 2.1 Hypervisors

As mentioned in chapter 1, a hypervisor is a virtual platform (similar to an OS [32]) that enables the creation of virtual machines (VM) in the same physical machine. The main purpose is to control VMs access to the machine resources [30] [10]. A hypervisor creates a virtual layer between the physical resources and the VMs (as also denoted "guests") so that each guest has a share of virtual hardware [32].

Currently there are multiple hypervisors, thus this section will discuss the main hypervisors (as well as Jailhouse): Xen and KVM.

#### 2.1.1 Hypervisor's Classification

Hypervisors can be divided in two types: type 1 and type 2 hypervisor. By definition, a type 1 is a bare-metal hypervisor that operates between hardware and the OS and a type 2 is considered as a hosting hypervisor, running above the OS [13].

Virtualization is a specific characteristic of the hypervisor technology and can be classified within two categories: (1) para-virtualized that uses a hypervisor as an abstraction layer between an OS and the hardware and which will imply modifications to the OS in order to communicate with the hypervisor and (2) full-virtualized which simulates the hardware from a machine and the guest OS does not need any modification [37].

Figure 2.1: Hypervisor's type 1 and 2 designs.

#### 2.1.2 The KVM Hypervisor

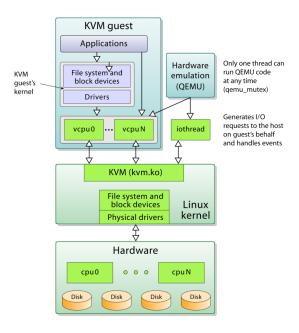

KVM, or Kernel-based Virtual Machine, is a virtualization technology, that transforms the Linux kernel into a hypervisor. The main advantage of this hypervisor is the ability to function alongside with the kernel and use kernel services, such as hard-disk write operations. It allows the hosting machine to launch multiple isolated virtual machines, by opening a device node named /dev/kvm [29], treating them as common Linux processes, as suggested by figure 2.2. Each guest has its own memory, separate from the userspace process that created it [29].

To use KVM one needs to enable virtualization in the target machine, requiring Intel processor with the Intel Virtualization Technology (VT) and the Intel 64 extensions or an Advance Micro Devices (AMD) processor with the AMD-V and the AMD64 extensions [7]. Then, two modules need to be loaded into the kernel: a host module and a processor-specific module; and an emulator. KVM takes advantage from being already part of the Linux kernel, because the kernel already has all components required to run VMs, such as memory manager or process scheduler [54]. All VMs share their resources and it is needed synchronization mechanisms in order to control

10

Figure 2.2: Basic architecture of the KVM Hypervisor.

resource's accesses.

KVM is not a traditional type 1 hypervisor since it transforms the Linux kernel into a hypervisor and it may seem that it provides system-level services (such as memory management), where is actually the kernel itself that provides them. It can be classified as a full-virtualized technology that can run multiple virtual machines executing unmodified Linux or Windows images [28].

#### 2.1.3 The Xen Hypervisor

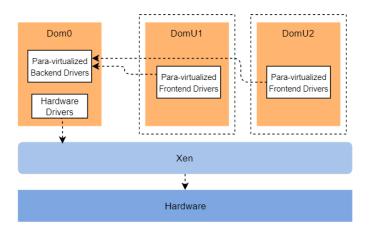

Xen is an open-source bare-metal hypervisor which enables the creation of multiple virtual machines called "domains". A privileged domain is created during boot, called dom0, and is responsible for creating another unprivileged domain, called domU. Once dom0 is shut down, the remaining domains will follow; however the opposite does not occur.

As suggested by figure 2.3, the dom0 is the only virtual machine that acts as an intermediate layer between Xen and the domU, being the only domain to interact directly with the hypervisor.

Both domains, privileged and unprivileged, are connected via para-virtualized drivers, called backend and frontend drivers, correspondingly, which gives dom0 a virtual device, visible to all other domains that it manages, and gives domU a device driver which will be used to establish the connection

Figure 2.3: Basic architecture of the Xen Hypervisor.

with dom0. The communication is established via shared memory.

Xen represents a more concise type 1 hypervisor, where the privileged domain is created during boot. One particularity of this hypervisor is that it can support both para-virtualization and full-virtualization [55].

#### 2.1.4 The Jailhouse Hypervisor

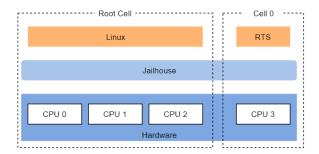

Jailhouse is a static partitioning hypervisor that runs with Linux, started by Jan Kiszka, a lead developer at Siemens, AG. In 2013, Siemens, AG. decided to open source it [5]. It manages partitions (called "cells"), where each one of them has a share of the computer resources, such as CPU, memory and PCI devices so, instead of having multiple guests accessing symmetrically to the resources and having no boundaries between them, Jailhouse divides the resources and assigns them to each partition, accordingly with their definitions. For instance, this hypervisor is meant to provide isolation between all partitions, such that there is no resource sharing and flexibility to run whatever software (called "inmates") they desire.

In order to launch the hypervisor, Linux is required to be installed on the system, because it is in charge of bootstrapping Jailhouse. After initialization, it is created an initial cell called the "root cell" and the hypervisor layer goes under the Linux layer. Originally, the root cell has to its possession

Figure 2.4: Basic architecture of a system using the Jailhouse Hypervisor.

all resources, but as more cells are created, defined resources are taken and assigned to the new cells. As demonstrated in figure 2.4, there are two cells: one root cell that runs Linux that has to its possession three CPUs and another non-root cell that run a RTOS with one CPU. In this case, if another cell were to be created with two defined CPUs, these resources would be taken from the root cell and assigned to the new cell, resulting in the root cell having 1 CPU, cell 0 having 1 CPU and the newer cell having two CPUs assigned.

Jailhouse does not fit in a standard hypervisor classification. It could be classified as a type 2 hypervisor, since it initially needs to be bootstrapped by Linux, but then, after initialization, the hypervisor goes under Linux and handles all operations, fitting in the type 1 description.

#### 2.2 Inter-VM Communication

Although one crucial requirement of this project is to necessarily implement IVSHMEM (shared-memory) as the mechanism of communication, there are some other viable options to take into account, as for instance a networking-based mechanisms such as TCP/IP protocol.

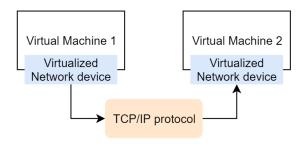

#### 2.2.1 TCP/IP-based Communication

TCP/IP is a networking communication protocol commonly used for nodes in different physical machines and can as well be used as a communication

Figure 2.5: Basic architecture of TCP/IP protocol.

channel between isolated virtual machines inside the same physical machines. The data is segmented into smaller chunks (or segments), wrapped into a packet and then delivered to a certain network node. It uses two different protocols: TCP (Transmission Control Protocol), which processes and receives data from sources; and IP (Internet Protocol) that provides addresses to each node of the network.

Figure 2.5 is a representation of how two virtual machines communicate using TCP/IP via a virtualized network device.

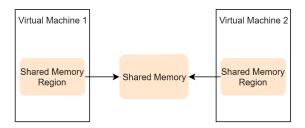

#### 2.2.2 Shared-Memory Communication

A traditional shared memory mechanism is translated into a specific region of memory that is mapped into several process's address space and configured by the OS resulting in a common area, visible by all of these processes. This methodology is considered to be the fastest and efficient inter-process communication mechanism [50], as suggested by figure 2.6 [8].

The main perk of using shared memory is to enable all processes to read and write directly from the memory region, where by using other methods, like TCP/IP based mechanisms, in general, there's a significant increase of overhead due to the fact that the same message has to go through multiple protocol layers.

Figure 2.6: Basic architecture of shared memory communication protocol.

## **IVSHMEM**

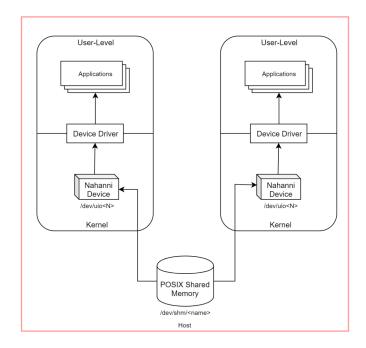

IVSHMEM (Inter-VM SHared MEMory), is an emulated PCI device that provides communication between co-located virtual machines (same host) by sharing memory establishing a connection between Portable Operating System Interface (POSIX<sup>1</sup>) shared memory on the Host and the application running inside a VM.

IVSHMEM's shared memory is visible to user-level code, which greatly simplifies the porting of existing libraries and supports pointer-based mechanisms [32] and its flexibility is proved by letting exist different memory regions between virtual machines, enforcing whatever policy is desired.

The virtual machines share the POSIX shared memory via series of mapping operations at the user level, with support for inter-VM interrupts via the Linux event file descriptor mechanism [32].

<sup>&</sup>lt;sup>1</sup>POSIX is a standard interface based on UNIX that facilitates software programs to be run in different machine's operating systems [38].

# 3. Jailhouse Hypervisor

This chapter is related to Jailhouse and gives a general view about the project and setup of the Jailhouse kernel module, including its hardware and software requirements. This hypervisor's functionality is explained in more technical detail, incorporating some examples implemented in an emulator called QEMU (using x86-64 architecture) and Banana Pi-M1 (ARM architecture).

# 3.1 Jailhouse Overview

As mentioned in section 1.1.1, Jailhouse is a hypervisor that follows the static hardware partitioning ideology that is based on the fact that partitions have their own share of the physical resources of the hardware available in the system and they are not shared.

Considering that this technology provides isolation between partitions, the system is prepared to safely run bare-metal partition without compromising any of their performances, which is why Jailhouse focuses primarily in giving exclusive access to the resources for each partition.

As suggested by figure 3.1, Linux is a fundamental piece for Jailhouse, in a way that the hypervisor is activated within its environment, taking over the hardware resources and moving under the OS, becoming the root cell. When Jailhouse creates a new cell (non-root cell), Jailhouse takes back

Figure 3.1: Jailhouse bootstrap process taken from [40].

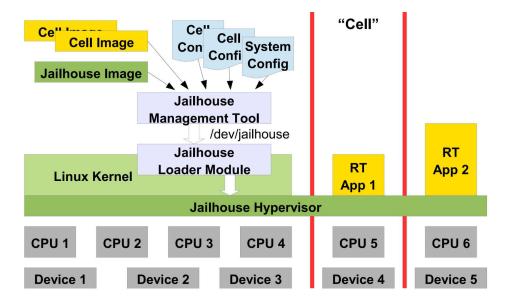

Figure 3.2: Jailhouse's system architecture taken from [14].

some resources allocated for the current root cell and assigns them to the new partition. These resources are explicitly defined in the configuration file for the new cell and includes a minimum of one CPU and a part of the memory from the root cell [40].

From all OSes, it is common to ask why Linux is the most suitable to perform this task. This OS is specially appropriate to Jailhouse's specification regarding hardware support [40], considering that it is one of the OSes that can be ran almost in every machine, which is very convenient and gives a major advantage to any developer who aims to explore the Jailhouse technology. Also, when directly assigning the devices, Jailhouse does not need device drivers, like other partitioning technologies (like Quest-V<sup>1</sup>), becoming lighter, system wise [40].

Figure 3.2 is a simple representation of Jailhouse's architecture, with two real-time applications, each one on their respective cell. The hypervisor

<sup>&</sup>lt;sup>1</sup>Quest-V is a static partitioning hypervisor that separates kernel into sandboxes, which are a security method for isolating different programs, and each one has a part of memory, I/O and CPU resources [57]

Figure 3.3: Jailhouse's package diagram.

works at the lowest-level possible with the support of a loadable kernel module (see section 4.1.2) which is in charge of managing the hypercalls<sup>2</sup> via a management tool.

# 3.1.1 Code Organization

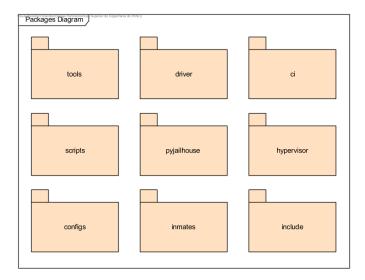

According to figure 3.3, Jailhouse's code repository is divided by 9 packages.

1. The ci, or continuous integration build environment package, is meant to help and adapt the current system's environment in order to run Jailhouse. Since every system has its own configuration, memory regions and hardware components, a static project like this hypervisor's can not demonstrate consistency in these terms, therefore some handy scripts to help configuration tasks were created. The configuration of the Linux kernel must allow some specific functionalities enabled to run and use Jailhouse smoothly. If the configuration file

<sup>&</sup>lt;sup>2</sup>A hypercall is a way to a user space application notify the OS that it needs to execute a command with higher priority [46]

(.config) in the kernel's source code is not synchronized with it, fixing the upcoming compilation/run time problems may be time consuming.

- 2. The pyjailhouse package is essentially a python module that extends Jailhouse's functionality [39].

- 3. The include package contains headers files.

- 4. The hypervisor package contains firmware specifics.

- 5. The scripts package contains version control scripts.

- 6. The driver package is related to the Jailhouse's loadable kernel module.

- The tools package contain the functionality scripts for all operations under Jailhouse. Its usage will be demonstrated in the next subsection.

- 8. The config package, as the name suggests, is where all configuration files for the cells are stored. Since the hypervisor is supported in 3 different architectures (arm, arm64 and x86), each one has its own compatible file so that the cells (root and non-root) are created within the boundaries of memory.

- The inmates package contains the software demonstrations that are meant to run within its equivalent cell. Each demo has different outputs.

#### 3.1.2 Jailhouse Requirements

In order to setup Jailhouse, two main components are required: Virtualization feature for I/O and virtualization extensions pack for the processor. This section is related to this hypervisor's requirements and their importance in the context of Jailhouse.

Intel Virtualization Technology, or Intel VT, is a general feature required to enable virtualization specifically for Intel-based systems [20]. It specializes in three different areas which are: CPU (focusing in virtual machines with native run time), memory (regarding direct memory access (DMA) remapping and extended page tables (EPT)) and I/O device support (related to the peripheral system, featuring Intel Virtualization Technology for Directed I/O (denoted as VT-d)) [20].

By using VT-d capabilities, the hypervisor is able to more efficiently manage the I/O inputs and outputs, physical memory and interrupt system [19], by allowing direct assignment to I/O ports. In other words, if a certain device is trying to access some block of memory which is not allowed to, then it will be blocked by the VT-d hardware which will contribute for the resource isolation featured by the Jailhouse hypervisor.

Virtual Machine Extensions (VMX or VT-x) and the equivalent for AMD systems, Secure Virtual Machine (SVM), are defined as extension packs for the processor in order to enable virtualization [2] and includes the following:

- EPT or Nested Page Tables (NPT): translates the physical addresses into guest physical addresses, granting the guest full control of its own page tables [1].

- 2. Unrestricted guest mode: determines if the guest will run in unpaged protected mode or in real address mode and will use EPT mechanism.

- 3. Preemption timer: mechanism that controls the preemption<sup>3</sup> of the guest VM's execution [2].

<sup>&</sup>lt;sup>3</sup>Preemption is switching a task for another with higher execution priority.

| x86-64 Architecture                                 |                            |                               |                       |  |

|-----------------------------------------------------|----------------------------|-------------------------------|-----------------------|--|

| Intel System                                        |                            | AMD System                    |                       |  |

| Intel Virtualization Technology                     |                            |                               |                       |  |

| Virtual<br>Machine<br>Extensions                    | Extended<br>Page Tables    | Secure<br>Virtual<br>Machines | Nested<br>Page Tables |  |

|                                                     | Unrestricted<br>Guest Mode |                               | Decode Assists        |  |

|                                                     | Preemption Timer           |                               |                       |  |

| Intel Virtualization Technology<br>for Directed I/O |                            | AMD IOMMU                     |                       |  |

| At least 2 logical CPUs                             |                            |                               |                       |  |

| ARM Architecture                                     |                                          |  |  |

|------------------------------------------------------|------------------------------------------|--|--|

| ARM Boards                                           | ARM64 Boards                             |  |  |

| Banana Pi                                            | AMD Seattle /<br>SoftIron Overdrive 3000 |  |  |

| Orange Pi Zero                                       | LeMaker HiKey                            |  |  |

| NVIDIA Jetson TK1                                    | NVIDIA Jetson TX1 and TX2                |  |  |

| ARM Versatile Express<br>with Cortex-A15 or A7 cores | Xilinx ZCU102                            |  |  |

| emtrion emCON-RZ/G1x series<br>based on Renesas RZ/G | NXP MCIMX8M-EVK                          |  |  |

| At least 2 logical CPUs                              |                                          |  |  |

| ARMv7 with virtualization extensions or ARMv8        |                                          |  |  |

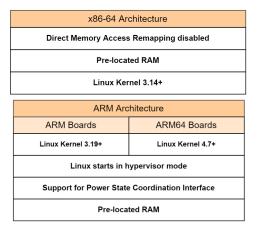

Figure 3.4: Jailhouse's hardware requirements for both architectures.

Jailhouse has also support for ARM and ARM64 architectures and figure 3.4 lists all boards that are currently available. All boards need at least 2 logical CPUs to run a root and non-root cell as well as for x86-64 architecture.

Jailhouse also has some specific software requirements. The hypervisor needs some pre-located RAM, in order to boot and re-allocated it to future cells [24]. For x86-64 architectures, I/O Memory Management Unit (IOMMU) has to be disabled as well and the minimum Linux kernel version is 3.14. For ARM and ARM64 architectures, the Linux kernel version must be at least 3.19 and 4.7 and Linux must start in hypervisor mode and has to support Power State Coordination Interface (PSCI).

22

Figure 3.5: Jailhouse's software requirements for both architectures.

#### 3.1.3 Linux Kernel Modules

The Linux kernel is an aggregation of pieces of executable code that are responsible for manipulating certain parts of the hardware. It can be split in 6 parts corresponding to the following [27]:

- Process management: responsible for taking into account the creation, manipulation and destruction of the Linux processes and the scheduler.

- Memory management: in charge of managing the whole memory system, including controlling the resource utilization of all software components.

- 3. **Filesystems:** this area is related to the multiple filesystems that Linux supports and how the data is organized.

- 4. Device control: this part refers to how hardware devices interact with the system. Traditionally, each device is mapped into the memory and is uniquely controlled by code, denoted as device driver. Since a device is at hardware level and an OS executes on top it, without a device driver to monitor the hardware, the communication between

device and OS would be non-existent and the operations sent to the device would not execute properly.

Networking: this area handles the networking aspects, for instance

if a system receives a packet, it must be identified and redirected to a

Linux process do handle it.

#### **Kernel Modules**

Loadable modules are out-of-tree kernel modules that are developed with the intent of extending the kernel's features and exploring their potential. Modules can be loaded and unloaded at any point during run time. After compiling a module against the desired kernel, the module results in an object file which is linked to the kernel after loading it [27].

To compile an out-of-tree module, usually a main-line kernel is more suitable to compile against since is free from heavy patches provided by developers [27]. The following commands will compile and install the module:

```

make KDIR=/path/to/source/kernel

make install

```

It is worth mention that if the compilation has not a explicit location of the desired Linux kernel, by default, the kernel module will be compiled with the already running kernel.

With an already compiled module, the next step is to load it into the kernel using one of the following:

```

modprobe "module"

insmod "module".ko

```

When the kernel module is loaded, that specific piece of code is inserted into the already existing kernel's code, translating it to symbol table of the kernel, enabling other lower-level functionalities. Both "modprobe" and "insmod" are the same functions regarding loading a module, but used in different matters. The first one will search in the desired kernel directory and

```

uio_ivshmem

jailhouse

sun4i_codec

16384

32768

49152

xp20x_pek

16384

snd_soc_core

snd_pcm_dmaengine

sun4i codec

155648

un4i backend

20480

sun4i_codec,snd_pcm_dmaengine,snd_soc_core

snd_pcm

snd timer,snd soc core,snd pcm

32768

61440

oundcore

16384

20480

sun4i_drm_hdmi

40960

sun4i drm hdmi

20480

usb_hdrc

sunxi

hygeneric

sun4i_drm

sun4i_frontend

sun4i_tcon

sun8i_tcon_top

16384

20480

16384

sun4i_drm,sun4i_backend

sun4i_drm

sun4i_drm,sun4i_tcon

32768

io_pdrv_genirq

16384

ivshmem,uio pdrv geniro

```

Figure 3.6: Loaded modules.

try to find the module and load all its dependencies, whereas the second one works with static paths and will not load any dependencies and so it can result in an "unresolved symbols" insertion error [27]. After succeeding, running "Ismod" command will list all inserted modules. Figure 3.6 represents the output of Ismod, which lists all inserted modules by designation, size in bytes and how many instances of the module are being used and by which component of the system [31]. One way to remove the module is running "rmmod" command which will fail in cases while the module is still in use.

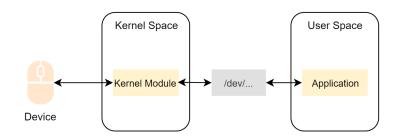

It will be created a device regarding the module that can be accessed within the /dev filesystem. Figure 3.7 is an example of how a device and an application are connected. User level applications will open the /dev filesystem which will give access to a kernel module and, consequently, control the device.

## 3.1.4 Jailhouse's Kernel Module

As mentioned in section 3.1, Jailhouse works with a loadable kernel module to issue hypercalls via a management tool denoted as jailhouse.ko.

Following section 3.1.3 command scheme, the kernel module is compiled

Figure 3.7: Kernel module transactions adapted from [15].

Figure 3.8: Jailhouse installation Makefile.

with the above command:

```

make KDIR=/path/to/source/kernel

```

The next step should be the installation of Jailhouse on target machine, by running the command below, which follows the defined rules of figure 3.8. All modules, firmware and tools will be installed.

```

make install

```

And the kernel module can be finally loaded into the kernel running one of the following commands:

```

modprobe jailhouse insmod jailhouse.ko

```

26

```

static void __attribute__((noreturn)) help(char *prog, int exit_status)

60 {

const struct extension *ext:

printf("Usage: %s { COMMAND | --help | --version }\n"

"\nAvailable commands:\n"

" enable SYSCONFIG\n"

" disable\n"

" console [-f | --follow]\n"

" cell create CELLCONFIG\n"

" cell list\n"

" cell load { ID | [--name] NAME } "

70

"{ IMAGE | { -s | --string } \"STRING\" }\n"

[-a | --address ADDRESS] ...\n"

" cell start { ID | [--name] NAME }\n"

" cell shutdown { ID | [--name] NAME }\n"

75

" cell destroy { ID | [--name] NAME }\n",

basename(prog));

for (ext = extensions; ext->cmd; ext++)

printf(" %s %s %s\n", ext->cmd, ext->subcmd, ext->help);

80

exit(exit_status);

81 }

```

Figure 3.9: Jailhouse's command line tool options.

# 3.1.5 Jailhouse Functionality

Figure 3.9 represents a piece of code from /tools/Jailhouse.c that prints a menu of available commands.

With the Jailhouse's kernel module already inserted (see section 3.1.2), the first thing to do is to enable the hypervisor by following the line 65 from figure 3.9:

```

jailhouse enable /path/to/system/configuration

```

The "enable" command from Jailhouse's management tool launches the hypervisor, passing multiple validations and creates the root cell, initializing all assigned CPUs and subsequently run it under Linux. Since the root cell will now be running with all of the resources as a whole, the next step is to create a cell configuration. Programs to be ran under a cell's environment can only use the resources that the cell makes accessible for them, nevertheless a cell configuration is needed to add and define resource's boundaries, including adding PCI devices.

The code below is an excerpt of a Jailhouse configuration file where the allocation of memory for RAM is described. It is defined a physical and virtual start addresses, the size and jailhouse's flags regarding read and write permissions. For more information of how to write a cell configuration file, consult sections B.1 and B.2 of the attachments.

One of the following command can be used (line 65 from figure 3.9):

```

jailhouse cell create /path/to/demonstration/cell/config

jailhouse config create my_config.c

```

The "cell create" is often used for pre-created cell configuration's. The "config create" is a cell configuration generator which is intended to generate files for both root and non-root cells. This command is highly useful when implementing Jailhouse in other potential environments, where the architecture may differ from what the hypervisor is used to. Since the assignment is based on memory ranges, configuration file depends on the hardware resources and memory boundaries. Next is loading the inmate inside the cell by following the command (line 70 from figure 3.9):

jailhouse cell load "demo\_name" /path/to/demonstration/cell/inmate This command line option usually requires that the inmate is specially created for the cell that is loaded into, because the cell configuration includes all hardware resources and sufficient memory allocation for the program to

run smoothly otherwise it may occur run time fails like "unhandled traps" (see section 3.1.5) or memory access's denials (see section 3.1.5). The next step is to finally launch the cell by following this command (line 73 from figure 3.9):

```

jailhouse cell start "demo_name"

```

The "cell start" splits the memory regions defined above of the root cell and assign them to the newly-created non-root cell, which will give it run-time isolation, that is, since the root cell no longer has control over the resources that the guest has allocated, then it no longer has permission to access them.

In order to stop or shutdown a cell, the command line option must be followed as (line 74 from figure 3.9):

```

jailhouse cell shutdown "demo_name"

```

And to destroy the cell (line 75 from figure 3.9):

```

jailhouse cell destroy "demo_name"

```

Certain cells have the ability to decline a shutdown request (see section 3.1.6). Although destroying a cell does not necessarily implies it, when those cells are running, the procedure to destroy them involves shutting down first then destroying it.

There are some control command line options to be used to check the state of the cells, i.e. the "cell list" option where it gives a list of the created cells, containing its identification (both numerical and by name), the loaded inmate (if it exists), the state and failed CPUs. The syntax is the following (line 69 from figure 3.9):

```

jailhouse cell list

```

Figure 3.10: Jailhouse's hypercall cell states.

#### 3.1.6 Jailhouse's Cell States

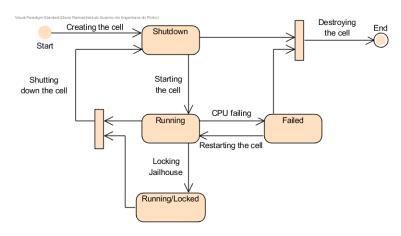

Accordingly to Jailhouse's hypercalls, defined in /include/jailhouse/hypercall header file (figure 3.10), there are 5 different cell states. Figure 3.11 is a state machine diagram that represents all the possible states and their outcomes for a non-root cell, that follows sequentially all the command tool options listed above.

When creating a cell configuration, the state is set to "shutdown", since there is already an empty cell, despite not being running. After loading and starting the cell, the state is changed to "running", considering the inmate is running and producing outputs. "Running/Locked" is an inevitable case which occurs when a cell is still running but locked its configuration so that no other cell (root and non-root) can modify it or when the hypervisor attempts to shutdown the cell. This last reason is an exception for cells that implement a voting system between all cells for certain operations such as shutting down, that is, if the hypervisor requests shutting down a cell, instead of having full control, other existing cells can vote and eventually decline it. Thus, a second try should succeed. "Failed" state is common where there are some run time fails, such as unhandled traps or parking errors, which leads to CPU failing (see section 3.1.6). For this particular state, there are two alternatives: restarting the cell, setting the state back to "running" or destroying it.

# 3.1.7 Run Time Failing Errors

As most technologies, Jailhouse is prepared to handle run time errors. According to figure 3.11, a certain cell can be set to a "failed" state, which

Figure 3.11: Jailhouse cell states.

normally can be lead by CPU suspension. These run-time errors are usually handled by macros called "traps". The hypervisor's trap occurs when it is trying to unsuccessfully map regions of memory. As mentioned above, the configuration files define boundaries of memory, not in a dynamic but hard-coded way. Those files are vulnerable for misconfiguration, considering that they need to be aligned with the memory for each physical device that it mentions.

There are two types of traps that are defined: unhandled and forbidden. The hypervisor passes through a bunch of validations. Figure 3.12 verifies the memory-mapped for the I/O (MMIO) accesses. In case where it results in either an MMIO\_ERROR or MMIO\_UNHANDLED values, the access is invalid. When trying to perform some sort of operation in memory regions that the hypervisor has not permissions, a forbidden trap appears. Accesses with appropriate permissions but not within the memory ranges will be caught as an unhandled trap. When operating on a cell with those conditions, it appears on the console some specific messages, implemented by figures 3.13 and 3.12.

Any trap leads the cell to a "failed" status. Since the CPU fails its initialization, the hypervisor suspends it and it no longer executes any code. The

```

451 case TRAP_FORBIDDEN:

452 panic_printk("FATAL: %s (exception class 0x%02x)\n",

453 (ret == TRAP_UNHANDLED? "unhandled trap":

454 "forbidden access"),

455 exception_class);

```

Figure 3.12: Jailhouse unhandled traps message.

```

98 error_unhandled:

99 panic_printk("Unhandled data %s at 0x%lx(%d)\n",

100 (is_write ? "write" : "read"), mmio.address, size);

101

102 return TRAP_UNHANDLED;

```

Figure 3.13: Jailhouse unhandled trap console message.

goal is to keep the CPU waiting until the hypervisor resets its status or destroys the cell. In addition to the triggering event and trap message, a special message (figure 3.15) appears indicating which CPU failed its execution (the one(s) assigned to the triggering cell) - parking. The message is based on "parking" a CPU, i.e., setting aside on execution, on panic, which is an OS safety measure when detecting an internal fatal error [48].

# 3.2 Jailhouse's Demonstrations

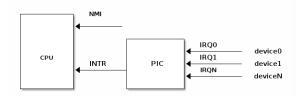

Jailhouse has some demonstration cells and this section is related to a QEMU based demonstration (apic-demo) implemented for Intel system x86-64 based architecture and an ARM architecture based demonstration (gic-demo).

```

mmio_result = mmio_handle_access(&mmio);

if (mmio_result == MMIO_ERROR)

return TRAP_FORBIDDEN;

if (mmio_result == MMIO_UNHANDLED)

goto error_unhandled;

```

Figure 3.14: Jailhouse unhandled traps conditions.

Figure 3.15: Jailhouse parking error.

Figure 3.16: QEMU architecture.

#### 3.2.1 QEMU Demonstration

QEMU, or Quick Emulator<sup>4</sup> is an emulation technology that runs virtual machines which can operate with KVM assistance and run under multiple systems such as x86, x86-64 and PowerPC and emulate numerous architectures like x86, x86-64, ARM, Scalable Processor ARChitecture (SPARC), PowerPC and Microprocessor without Interlocked Pipeline Stages (MIPS) [45].

KVM is a kernel module that is loaded into the Linux kernel in order to transform it into a hypervisor and is an important piece in QEMU. With hardware capable of using virtualization, i.e. VT-d or AMD-v, QEMU can

<sup>&</sup>lt;sup>4</sup>An emulator is generally a program or device that enables the creation of a different environment within a machine, by creating its particular hardware components.

create user-space virtual machines that will be taken care of with the current hypervisor's help [18].

Figure 3.16 shows that QEMU emulates hardware and can benefit from supporting KVM, i.e. creates Virtual CPUS (VCPUs) in order to execute the intended code on the guests side. Guests are created as KVM guests that are intended to run software and communicate with VCPUs which communicates with the KVM interface inserted in the actual kernel. This emulator also sends I/O requests to the kernel module so that events regarding its virtual machines are handled.

# Setting up Jailhouse with QEMU

For demonstration purposes and software validation, using an emulator such as QEMU to run Jailhouse is appropriate. Since the QEMU already provides all possible hardware devices that the hypervisor might need, this is a way to run Jailhouse almost in any environment at any time without compromising the machine itself. There are already some demonstration cells ready-to-use in multiple architectures like x86-64, arm64, arm, etc.

The first step is to get QEMU working properly. An updated version of this emulator is recommended and can be extracted by the main QEMU page (https://www.qemu.org/download/source).

The configuration script that QEMU provides, by default, builds it with every available architecture. Therefore a target list must be defined, in this case a x86-64 architecture. The Simple DirectMedia Layer (SDL) option is enabled in order to have a graphical display mode, otherwise if no display is enabled, the emulator will start and hangs at the Virtual Network Computing (VNC) server<sup>5</sup>.

```

./configure -target-list=x86-64-softmmu -enable-sdl make

```

<sup>&</sup>lt;sup>5</sup>The VNC server is a remote way for a user to access another machine.

make install

Now that QEMU is installed, there are two paths to follow to run Jailhouse:

Setting up and running the hypervisor with the assistance of a side repository.

By following the first approach, the first step is to clone the "Jailhouseimages" side repository using the git tool:

```

git clone https://github.com/siemens/jailhouse-images.git

```

The host machine must fulfill the following requirements [25]:

- (a) Updated Docker, which will create containers that will allow the demonstrations to run isolated, that is, the applications will not be able to see more than the resources assigned to their container:

- (b) QEMU version must be equal or higher than 2.8 for x86 image and higher or equal than 2.12 for ARM64 image;

- (c) Linux kernel version above or equal to 4.4 with KVM support (for x86 image);

- (d) On Intel, kvm\_intel module loaded with parameter nested=1. This parameter will enable nested virtualization and permit that inside a KVM virtual machine it can run a hypervisor [36].

This repository has two main parts: the build-images and the start-qemu script. In order to QEMU initialize, it needs an image prepared by the first script which allows the build for multiple environments (figure 3.17). In this particular case, the QEMU/KVM Intel-x86 virtual target is selected as the emulator to configure for this type of systems. The second script initializes the emulator with the built image (Linux kernel 4.19.56) and already display a bunch of usable ordered

```

1: QEMU/KVM Intel-x86 virtual target

2: QEMU ARM64 virtual target

3: Orange Pi Zero (256 MB edition)

4: Intel NUC (NUC6CAY, 8 GB RAM)

5: Marvell ESPRESSObin (1 GB edition)

6: Marvell MACCHIATObin

7: LeMaker HiKey (Kürin 620 SoC, 2 GB edition)

8: Avnet Ultra96

0: all (may take hours...)

```

Figure 3.17: QEMU images list.

```

jailhouse enable /etc/jailhouse/qemu-x86.cell

jailhouse console

jailhouse cell create /etc/jailhouse/apic-demo.cell

jailhouse cell load apic-demo /usr/libexec/jailhouse/demos/apic-demo.bin

jailhouse cell start apic-demo

jailhouse cell stats apic-demo

jailhouse cell destroy apic-demo

jailhouse cell linux /etc/jailhouse/linux-x86-demo.cell /boot/vmlinuz* \

-i /usr/libexec/jailhouse/demos/rootfs.cpio \

-c "console=tty50 8250.nr_uarts=1 ip=192.168.19.2"

ssh 192.168.19.2

jailhouse disable

```

Figure 3.18: Bash history for QEMU's AMD systems.

command line options (located in the history 3.18) to run Jailhouse and work with apic-demo cell and a non-root Linux cell.

```

./build-images

./start-qemu "architecture"

```

2. Starting a virtual machine from scratch, build Jailhouse and run: